# PHY(IEEE 1394) MD8405E

ユーザーズマニュアル

# **MEMO**

# 改版履歴

| 版数   | 日付               | 改版内容                                |

|------|------------------|-------------------------------------|

| 1.00 |                  |                                     |

| 1.00 | 平成 11 年 5 月 28 日 | MD8405E 対応新規                        |

| 1.01 | 平成 11 年 6月 23 日  | Register17 記述ミス修正                   |

|      |                  | 10-1 MD8404 とのピン互換記述ミス修正            |

|      |                  | 10-2 MD8405B / MD8405D とのピン互換記述ミス修正 |

| 1.03 | 平成 11 年 8 月 25 日 | 2-2 端子の機能説明記述ミス修正                   |

|      |                  | 図 8-1 外形寸法図修正                       |

# 凡例

データの MSB,LSB : 左が MSB、右が LSB

**負論理信号の記述**:信号名の最後に#が付けられているもの

**数の記述** : 2 進数 \*\*\*\*b または \*\*\*\*

10 進数 \*\*\*\* 16 進数 \*\*\*\*h

**用語** : Byte 8 ビット幅のデータ

Word

16 ビット幅のデータ

Quadlet

32 ビット幅のデータ

Octlet

64 ビット幅のデータ

注: MD8404 までは PC[0:2] 端子で PC2 が MSB、PC0 が LSB の記述となっておりました。MD8405 以降はこれを修正し、PC0 が MSB、PC2 が LSB とします。ハード的には変更しない為、MD8405 のピン配置では MD8404 と比べて PC0 と PC2 が入れ替わっております。PHY では今後、MD8405 を含めてデータ番号の小さい方 (例えば "0") が MSB、データ番号が大きい方 (例えば "7") を LSB に統一します。

#### MD8405B からの変更点

MD8405E では、P1394a Draft Ver2.0 規格にある BIAS\_HANDSHAKE\_TIME を変更できるよう機能を追加しております。

#### 変更点

- ・Register71 に EnDV ビットを追加。このビットの初期値は "1"。このビットの状態で BIAS HANDSHAKE TIME 値を変更可能としています。

- ・Register17 の値が 62h から 65h に変更

#### MD8405C からの変更点

MD8405E では、MD8405C で En\_DV 端子にしていたものを MD8405B と同様に En\_Multi 端子にもどしました。 これによって Register71 の EnDV ビットを初期値 "1" としています。

#### MD8405D からの変更点

1. バグ修正

MD8405D のエラッタにある以下の項目を修正。

- 1.1 TpBias Down

- 1.2 Suspend Fault (S/R="H"のみ)

- 1.3 Resume Fault (S/R="H"のみ)

- 1.4 SefID 受信

- 1.5 gap count

- 1.6 EnDV

- 2. Product ID

Product ID レジスタ値を 0x303565(05e) に修正。

# 関連資料

IEEE Std 1394-1995 Standard for a High Performance Serial Bus IEEE P1394a Draft 2.0 Standard for a High Performance Serial Bus

# ライセンス

当社は、SGS-Thomson Microelectronics 社から同社所有の IEEE1394 High Performance Serial Bus Standard に関する特許の使用ライセンスを受けております。

# **MEMO**

# 目次

| 1 | 概要  |                                              | 1  |

|---|-----|----------------------------------------------|----|

|   | 1-1 | 特徵                                           | 1  |

|   | 1-2 | 用途                                           | 1  |

|   | 1-3 | 内部プロック図                                      | 2  |

|   |     |                                              |    |

| 2 |     | 明                                            |    |

|   | 2-1 | 端子配列                                         |    |

|   | 2-2 | 端子の機能説明                                      | 4  |

| 3 | コント | ロールレジスタ                                      | 7  |

|   | 3-1 | レジスタアクセス方法                                   |    |

|   | 3-2 | レジスタ内容                                       | 7  |

|   |     | 3-2-1 Register0                              | 7  |

|   |     | 3-2-2 Register1                              | 7  |

|   |     | 3-2-3 Register2                              | 8  |

|   |     | 3-2-4 Register3                              | 8  |

|   |     | 3-2-5 Register4                              | 8  |

|   |     | 3-2-6 Register5                              | 9  |

|   |     | 3-2-7 Register6                              | 10 |

|   |     | 3-2-8 Register7                              | 10 |

|   | 3-3 | レジスター覧                                       | 11 |

|   | 3-4 | Page_select=0 ( Port Status page )           | 12 |

|   |     | 3-4-1 Register00                             | 12 |

|   |     | 3-4-2 Register01                             | 12 |

|   |     | 3-4-3 Register02                             | 13 |

|   |     | 3-4-4 Register03                             | 13 |

|   |     | 3-4-5 Register04                             | 13 |

|   |     | 3-4-6 Register05                             | 14 |

|   |     | 3-4-7 Register06                             | 14 |

|   |     | 3-4-8 Register07                             | 14 |

|   | 3-5 | Page_select=0 一覧                             | 15 |

|   | 3-6 | Page_select=1 ( Vendor Identification page ) | 16 |

|   |     | 3-6-1 Register10                             | 16 |

|   |     | 3-6-2 Register11                             | 16 |

|   |     | 3-6-3 Register12                             | 16 |

|   |     | 3-6-4 Register13                             | 16 |

|   |     | 3-6-5 Register14                             | 17 |

|   |     | 3-6-6 Register15                             | 17 |

|   |     | 3-6-7 Register16                             | 17 |

|   |     | 3-6-8   | Register17                             | 17 |

|---|-----|---------|----------------------------------------|----|

|   | 3-7 | Page_se | lect=1 一覧                              | 18 |

|   | 3-8 | Page_se | elect=7 ( Vendor Dependent page )      | 19 |

|   |     | 3-8-1   | Register70                             | 19 |

|   |     | 3-8-2   | Register71                             | 19 |

|   |     | 3-8-3   | Register72                             | 19 |

|   |     | 3-8-4   | Register73                             | 19 |

|   |     | 3-8-5   | Register74                             | 20 |

|   |     | 3-8-6   | Register75                             | 20 |

|   |     | 3-8-7   | Register76                             | 20 |

|   |     | 3-8-8   | Register77                             | 20 |

|   | 3-9 | Page_se | lect=7 一覧                              | 21 |

| 4 | データ | フォーマ    | ψ <b>-</b>                             | 22 |

|   | 4-1 | Self-ID | Packet                                 | 22 |

|   | 4-2 | Link-on | Packet                                 | 23 |

|   | 4-3 | PHY Co  | onfiguration Packet                    | 23 |

|   | 4-4 | Extende | d PHY Packet                           | 23 |

|   |     | 4-4-1   | Ping Packet                            | 23 |

|   |     | 4-4-2   | Remote Access Packet                   | 24 |

|   |     | 4-4-3   | Remote Reply Packet                    | 24 |

|   |     | 4-4-4   | Remote Command Packet                  | 24 |

|   |     | 4-4-5   | Remote Confirmation Packet             | 24 |

|   |     | 4-4-6   | Resume Packet                          | 24 |

| 5 | 機能説 | 明       |                                        | 25 |

|   | 5-1 | Link チ  | ップインターフェイス                             | 25 |

|   |     | 5-1-1   | 接続方法                                   | 25 |

|   |     |         | 5-1-1-1 DC 接続                          | 25 |

|   |     |         | 5-1-1-2 AC 接続                          | 25 |

|   |     | 5-1-2   | LPS(Link Power Status)                 | 26 |

|   |     | 5-1-3   | LinkOn                                 | 27 |

|   |     | 5-1-4   | Link インターフェイス ( LREQ、CTL[0:1]、D[0:7] ) | 27 |

|   |     |         | 5-1-4-1 LREQ                           | 28 |

|   |     |         | 5-1-4-2 Status 出力                      | 31 |

|   |     |         | 5-1-4-3 Transmit.                      | 32 |

|   |     |         | 5-1-4-4 Receive                        |    |

|   |     |         | 5-1-4-5 Link インターフェイス初期化動作             | 35 |

|   |     | 5-1-5   | DIRECT                                 | 36 |

|   |     | 5-1-6   | LDSEL                                  |    |

|   |     | 5-1-7   | アイソレーションバリア                            |    |

|   | 5-2 | ケーブ     | ルインターフェイス                              |    |

|   |     | 5-2-1   | ケーブルインターフェイス回路                         | 41 |

|                  |      | 5-2-2  | ケーブルインターフェイス動作概要                    | 42         |

|------------------|------|--------|-------------------------------------|------------|

|                  |      | 5-2-3  | ポートステート                             | 44         |

|                  |      | 5-2-4  | コネクト検出回路                            | 44         |

|                  |      | 5-2-5  | Suspend/Resume                      | 44         |

|                  |      | 5-2-6  | Suspend/Resume オフモード ( SR 端子 ="L" ) | 45         |

|                  |      | 5-2-7  | 低消費電力 ( Power Down ) モード            | 46         |

|                  |      | 5-2-8  | S200 モード ( S200 端子 ="H" )           | 46         |

|                  |      | 5-2-9  | CPS ( ケーブルパワーステータス )                | 46         |

|                  |      | 5-2-10 | ) 未使用ポートの処理                         | 47         |

|                  | 5-3  | クロック   | ク回路                                 | 48         |

|                  |      | 5-3-1  | クリスタルオシレータ                          | 48         |

|                  |      | 5-3-2  | PLL                                 | 48         |

|                  | 5-4  | 外部回路   | 路                                   | 48         |

|                  |      | 5-4-1  | CPS 端子                              | 48         |

|                  |      | 5-4-2  | Rext 端子                             | 49         |

|                  |      | 5-4-3  | Vref 端子                             | 49         |

|                  | 5-5  | ハードワ   | ウェアリセット                             | 50         |

| 6                | 電気特  | 性      |                                     | 51         |

|                  | 6-1  | 絶対最大   | 大定格                                 | 51         |

|                  | 6-2  | 推奨動作   | 作条件                                 | 51         |

|                  | 6-3  | DC 特性  | <u> </u>                            | 52         |

|                  | 6-4  | AC 特性  | ±                                   | 54         |

| 7                | 推奨回题 | 路図     |                                     | 57         |

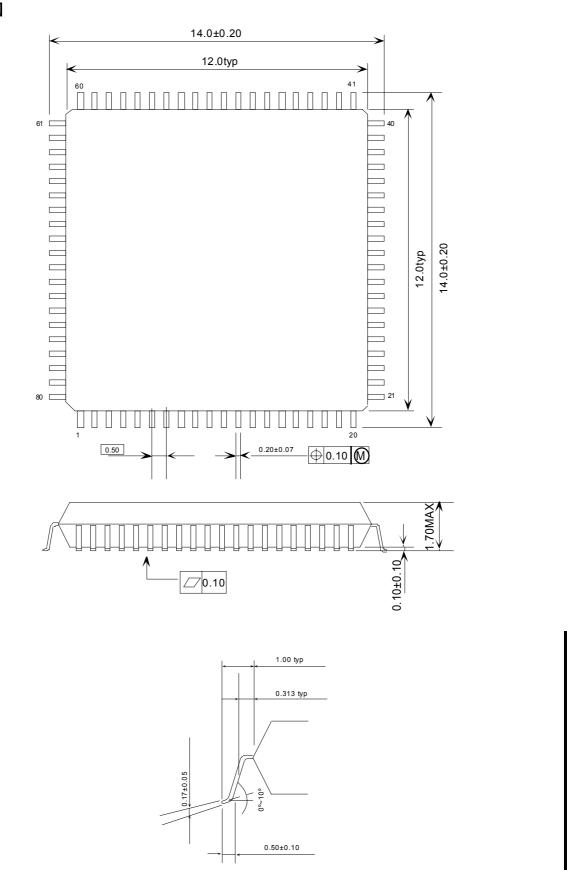

| 8                | 外形図  |        |                                     | 59         |

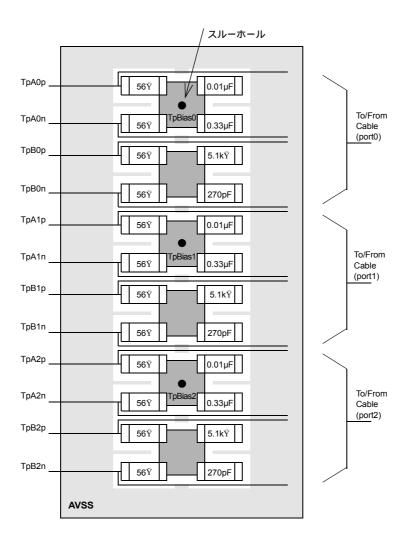

| 9                | 部品配  | 置      |                                     | 60         |

| 10               | ピン互  | 換性     |                                     | 6          |

|                  | 10-1 | MD8404 | 4 とのピン互換                            | 61         |

|                  | 10-2 | MD8405 | 5B / MD8405D とのピン互換                 | 61         |

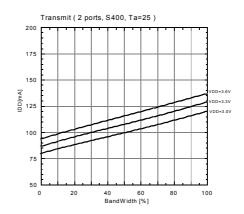

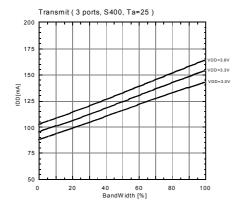

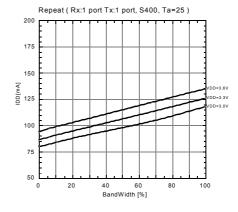

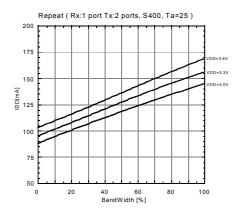

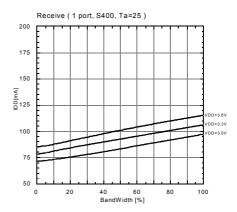

| 11               | 付録 A | 送受信    | 条件における消費電流(代表値)                     | 62         |

| ; <del>†</del> : | 音車百  |        |                                     | <i>L</i> ? |

# 図表目次

| 図 1-1  | MD8405 のブロック図                            | 2  |

|--------|------------------------------------------|----|

| 図 2-1  | 端子配列図                                    | 3  |

| 図 4-1  | Self-ID パケットフォーマット                       | 22 |

| 図 4-2  | Link-on パケットフォーマット                       | 23 |

| 図 4-3  | PHY Configuration パケットフォーマット             | 23 |

| 図 4-4  | Ping パケットフォーマット                          | 23 |

| 図 4-9  | Resume パケットフォーマット                        | 24 |

| 図 4-5  | Remote Access パケットフォーマット                 | 24 |

| 図 4-6  | Remote Reply パケットフォーマット                  | 24 |

| 図 4-7  | Remote Command パケットフォーマット                | 24 |

| 図 4-8  | Remote Confirmation パケットフォーマット           | 24 |

| 図 5-1  | MD8405 と Link チップの接続図(DC 接続)             | 25 |

| 図 5-2  | MD8405 と Link チップの接続図(AC 接続)             | 25 |

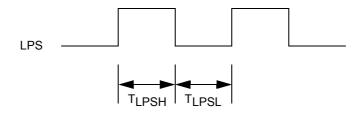

| 図 5-3  | AC 接続時の LPS 波形                           | 26 |

| 図 5-4  | LREQ ストリーム                               | 28 |

| 図 5-5  | Status                                   | 31 |

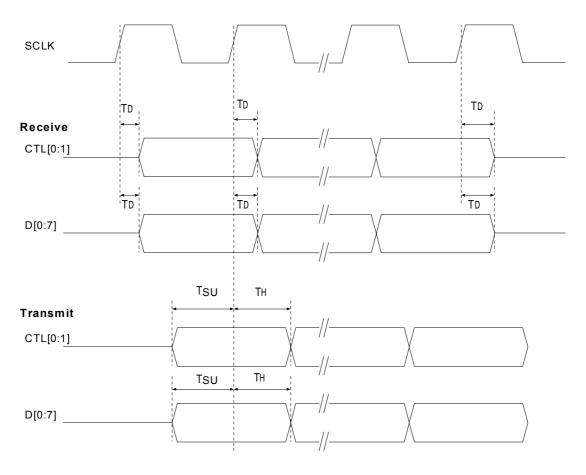

| 図 5-6  | Transmit                                 | 32 |

| 図 5-7  | Receive                                  | 34 |

| 図 5-8  | AC 接続時の PHY/Link インターフェイス初期化             | 35 |

| 図 5-9  | DC 接続時の PHY/Link インターフェイス初期化             | 35 |

| 図 5-10 | IEEE P1394a Draft Ver2.0 アイソレーションバリア(一例) | 36 |

| 図 5-11 | ドライバ回路「微分」出力波形                           | 37 |

| 図 5-12 | アイソレーションバリア回路                            | 37 |

| 図 5-13 | 各ノードの波形例                                 | 38 |

| 図 5-14 | LREQ アイソレーションバリア回路                       | 39 |

| 図 5-15 | LPS アイソレーションバリア回路                        | 39 |

| 図 5-16 | SCLK アイソレーションバリア回路                       | 39 |

| 図 5-17 | CTL[0:1] アイソレーションバリア回路                   | 40 |

| 図 5-18 | D[0:7] アイソレーションバリア回路                     | 40 |

| 図 5-19 | VSS 接続                                   | 40 |

| 図 5-20 | ケーブルインターフェイス                             | 41 |

| 図 5-21 | ドライバ電流と出力波形 (S200 スピードシグナル時 )            | 43 |

| 図 5-22 | 1 ポートのみ使用時回路図                            | 47 |

| 図 5-23 | クロック回路                                   | 48 |

| 図 5-24 | PLL 外部回路                                 | 48 |

| 図 5-25 | CPS 外部回路                                 | 48 |

| 図 5-26 | Rext 外部回路                                | 49 |

| 図 5-27 | Vref 外部回路                                | 49 |

| 図 6-1  | Link インターフェイス AC 特性 ( SCLK,Link-On )     | 54 |

| 図 6-2  | Link インターフェイス AC 特性 ( CTL,D ) | 55 |

|--------|-------------------------------|----|

| 図 6-3  | Link インターフェイス AC 特性 ( LREQ )  | 55 |

| 図 6-4  | クロックタイミング                     | 55 |

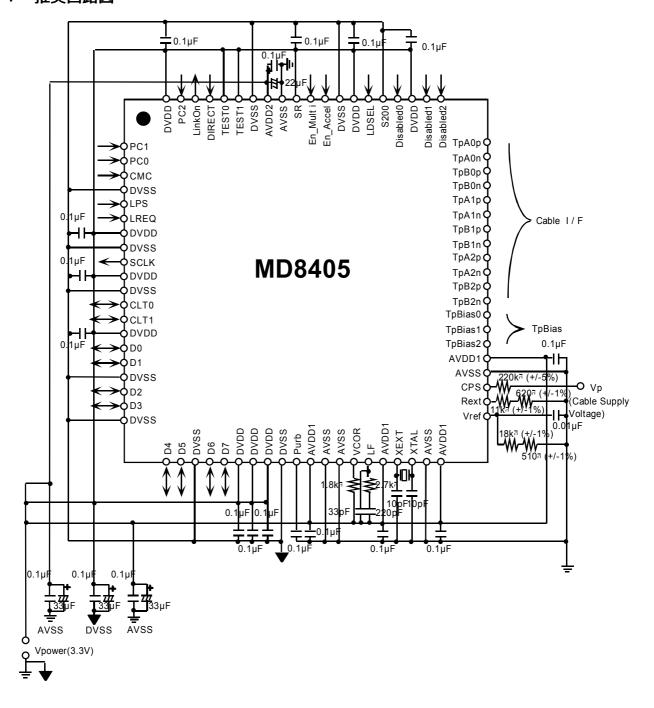

| 図 7-1  | MD8405 推奨回路図(例)               | 57 |

| 図 7-2  | ケーブルインターフェイス接続推奨回路図           | 58 |

| 図 8-1  | 外形寸法図                         | 59 |

| 図 9-1  | 部品配置参考図                       | 60 |

| 表 2-1  | MD8405 端子表 (1)                | 4  |

| 表 2-2  | MD8405 端子表 (2)                | 5  |

| 表 2-3  | MD8405 端子表 (3)                | 6  |

| 表 3-1  | レジスター覧表                       | 11 |

| 表 3-2  | page_select=0 一覧表             | 15 |

| 表 3-3  | page_select=1 一覧表             | 18 |

| 表 3-4  | page_select=7 一覧表             | 21 |

| 表 5-1  | LPS タイミング                     | 26 |

| 表 5-2  | PHY が CTL を制御する動作             | 27 |

| 表 5-3  | Link が CTL を制御する動作            | 27 |

| 表 5-4  | Request フォーマット                | 28 |

| 表 5-5  | Speed フォーマット                  | 28 |

| 表 5-6  | Read Register フォーマット          |    |

| 表 5-7  | Write Register フォーマット         | 29 |

| 表 5-8  | アクセラレーションコントロールフォーマット         | 29 |

| 表 5-9  | Request Type                  | 29 |

| 表 5-10 | Status フォーマット                 | 31 |

| 表 5-11 | スピードコード (SP[0:7])             | 34 |

| 表 5-12 | Link インターフェイス初期化動作            | 35 |

| 表 5-13 | 未使用ポート端子の処理                   | 47 |

| 表 6-1  | 絶対最大定格                        | 51 |

| 表 6-2  | 推奨動作条件                        | 51 |

| 表 6-3  | DC 特性 ( Link インターフェイス )       | 52 |

| 表 6-4  | DC 特性 ( ケーブルインターフェイス )        |    |

| 表 6-5  | AC 特性 ( Link インターフェイス )       | 54 |

| 表 6-6  | AC 特性 ( ツイストペアインターフェイス )      | 54 |

| 表 6-7  | クロック回路 AC 特性                  | 56 |

| 表 10-1 | MD8405E 動作                    | 61 |

# **MEMO**

# 1 概要

MD8405 は、IEEE P1394a Draft Ver2.0 に準拠した 400/200/100Mbit/sec の転送スピードをサポートする物理層 IC です。1394 ケーブルインターフェイス用の 3 つのポート、リンク層 IC へのインターフェイス、バス初期化とアービトレーションのためのステートマシンロジックを持ち合わせています。MD8405 は IEEE P1394a Draft Ver2.0 プロトコルの物理層ファンクション、リンク層インターフェイスをサポートします。

#### 1-1 特徴

IEEE P1394a Draft Ver2.0 に準拠する低電圧振幅差動トランシーバ

393.216Mbit/sec , 196.608Mbit/sec と 98.304 Mbit/sec のデータレートをサポート

393.216 MHz PLL 内蔵

パワーセーブの為の、停止ポートに対する自動シャットダウン機能

3 ポート独立した TpBias

ケーブル電源の低下を Cable Power Status により検出

P1394a Draft Ver2.0 に準拠したバス 初期化、アービトレーションの為のステートマシーンロジック

P1394a Draft Ver2.0 に準拠した Port connection ステートマシーン

P1394a Draft Ver2.0 に準拠した PHY/Link インターフェイス

DC、AC 接続による PHY-Link インターフェイスをサポート

PHY-Link インターフェイス AC タイミング設定端子

各ポート毎に設定可能な Disabled 設定ピンのサポート

En Accel、En Multi 設定ピンのサポート

Configuration Manager Capable、PowerClass 定義ピンのサポート

#### 1-2 用途

デジタルカメラ デジタル VCR デジタルオーディオ 電子楽器 スキャナ プリンタ

各種ストレージ

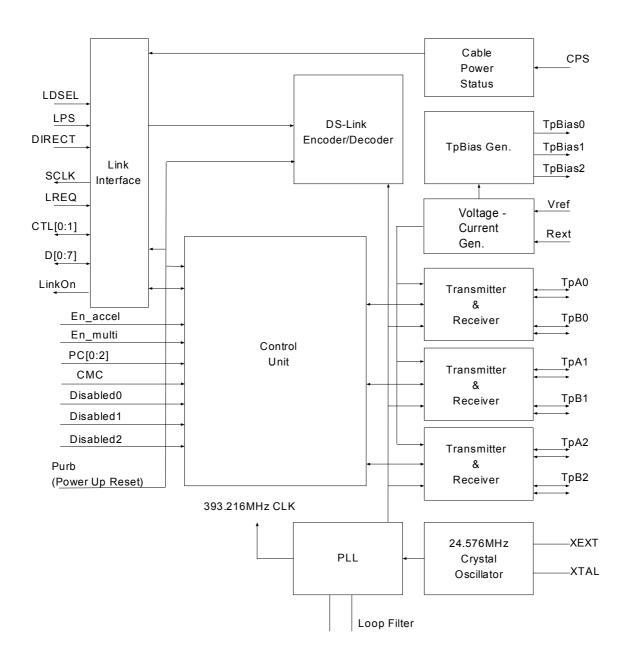

#### 1-3 内部プロック図

図 1-1 MD8405 のブロック図

# 2 端子説明

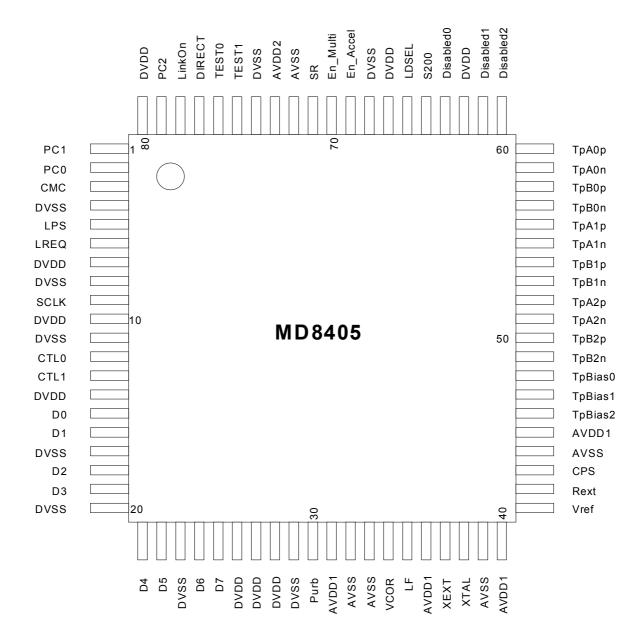

#### 2-1 端子配列

図 2-1 端子配列図

# 2-2 端子の機能説明

| ピン番号               | ピン名      | I/O | 機能                                                         |

|--------------------|----------|-----|------------------------------------------------------------|

| 2,1,79             | PC[0:2]  | I   | Power Class[0:2]。                                          |

|                    |          |     | PHY レジスタアドレス 4 の Pwr_class ビットのハードウエアリセット初期値               |

|                    |          |     | としてこの端子の状態を反映。                                             |

|                    |          |     | 設定により DVDD 又は、DVSS に接続。                                    |

| 3                  | CMC      | I   | Configuration Management Capable 接続端子。                     |

|                    |          |     | PHY レジスタアドレス 4 の Contender ビットのハードウエアリセット初期値               |

|                    |          |     | として反映。                                                     |

| 4,8,11,17,20,23,   | DVSS     | -   | デジタルグランド。                                                  |

| 29,68,74,          |          |     |                                                            |

| 5                  | LPS      | I   | Link Power Status。Link がアクティブかどうかをモニター。                    |

|                    |          |     | [5-1-2 参照 ]                                                |

| 6                  | LREQ     | I   | Link Request。Link が LREQ 端子により PHY レジスタの                   |

|                    |          |     | リード / ライト、バスリクエストを行う。                                      |

|                    |          |     | [5-1-4 参照]                                                 |

| 7,10,14,26,27,28,  | DVDD     | -   | デジタル電源。                                                    |

| 63,67,80           |          |     |                                                            |

| 9                  | SCLK     | 0   | 49.152MHz Link システムクロック。                                   |

|                    |          |     | PHY-Link インターフェイス、ケーブルインターフェイスは                            |

|                    |          |     | SCLK に同期。                                                  |

| 12,13              | CTL[0:1] | I/O | PHY-Link インターフェイス制御信号。                                     |

|                    |          |     | [5-1-4 参照]                                                 |

| 15,16,18,19,21,22, | D[0:7]   | I/O | PHY-Link インターフェイスデータ信号。                                    |

| 24,25              |          |     | [5-1-4 参照]                                                 |

| 30                 | Purb     | ı   | Power Up Reset 用外部コンデンサ接続端子。                               |

|                    |          |     | 0.1[μF] を介して DVSS へ。                                       |

|                    |          |     | リセット期間は最小 15[msec]。リセット期間中、内部ステート                          |

|                    |          |     | マシーンは、すべて初期化される。                                           |

|                    |          |     | [5-4 参照 ]                                                  |

| 65                 | S200     | I   | スピード切り替え端子。                                                |

|                    |          |     | "H": S200 として動作。                                           |

|                    |          |     | "L": S400 として動作。                                           |

|                    |          |     | 通常は "L"。                                                   |

| 71                 | SR       | I   | Suspend/Resume 機能切り替え端子。                                   |

|                    |          |     | "H" で P1394a Draft Ver2.0 準拠。                              |

|                    |          |     | "L" のとき P1394a Draft Ver1.3 準拠。この為 Suspend/Resume 機能は OFF。 |

|                    |          |     | 通常は "H"。                                                   |

|                    |          |     |                                                            |

表 2-1 MD8405 端子表 (1)

| ピン番号           | ピン名           | I/O | 機能                                                               |  |

|----------------|---------------|-----|------------------------------------------------------------------|--|

| 31,36,40,45    | AVDD1         | -   | アナログ電源 1。                                                        |  |

|                |               |     | ケーブルインターフェイスドライバ用電源以外の電源。                                        |  |

| 32,33,39,44,72 | AVSS          | -   | アナロググランド。                                                        |  |

| 34             | VCOR          | I   | 外部ループフィルタ接続端子。                                                   |  |

| 35             | LF            | 0   |                                                                  |  |

| 37,38          | XEXT, XTAL    | I/O | クリスタル接続。水晶発振子接続端子。                                               |  |

|                |               |     | オシレータ出力周波数は 24.576MHz±100ppm が必要。                                |  |

|                |               |     | 使用される水晶発振子自身は、10[pF] の負荷を接続した状態で                                 |  |

|                |               |     | ±50ppm の精度が必要。                                                   |  |

|                |               |     | [5-3 参照 ]                                                        |  |

| 41             | Vref          |     | がは株式やなない。                                                        |  |

| 71             | VICI          | '   | 外部基準抵抗接続端子。<br>  外部抵抗 18[kΩ]+510[Ω] (±1%) 及び 0.01μF を AVSS 間に接続。 |  |

|                |               |     |                                                                  |  |

| 42             | Rext          | l I | 外部基準抵抗接続端子。<br>                                                  |  |

|                |               |     | 外部抵抗 11[kΩ]+620[Ω] (±1%) を AVSS 間に接続。                            |  |

| 43             | CPS           | I   | CablePowerStatus 検出用端子。                                          |  |

|                |               |     | 220(±5%)[kΩ] を介して Cable Power(Vp) へ接続。                           |  |

|                |               |     | 未使用時は、AVDD1 に接続。                                                 |  |

|                |               |     | [5-2-9 参照 ]                                                      |  |

| 46,47,48       | TpBias[2:0]   | 0   | <br> ケーブルバイアス出力端子。                                               |  |

| , ,            |               |     | 0.33[μF] を介して AVSS へ接続。                                          |  |

| 49,53,57       | TpB[2:0]n     | I/O | Arbitration/Speed Signal/Data 出力、                                |  |

|                |               |     | Arbitration/Strobe 入力。逆相入出力端子。                                   |  |

| 50,54,58       | TpB[2:0]p     | I/O | Arbitration/Speed Signal/Data 出力、                                |  |

| 00,04,00       | 1 65[2.0]6    |     | Arbitration/Strobe 入力。正相入出力端子。                                   |  |

| 54.55.50       | T 410 01      | 1/0 |                                                                  |  |

| 51,55,59       | TpA[2:0]n     | I/O | Arbitration/Strobe 出力、                                           |  |

|                |               |     | Arbitration/Speed Signal/Data 入力。逆相入出力端子。                        |  |

| 52,56,60       | TpA[2:0]p     | I/O | Arbitration/Strobe 出力、                                           |  |

|                |               |     | Arbitration/Speed Signal/Data 入力。正相入出力端子。                        |  |

| 61,62,64       | Disabled[2:0] | I   | PHY レジスタポートステータスページの Disabled ビットのハード                            |  |

|                |               |     | ウエアリセット初期値としてこの端子の状態を反映。                                         |  |

|                |               |     | [3-4-1 Bit 7 参照 ]                                                |  |

| 66             | LDSEL         | I   | │<br>│PHY-Link インターフェイスタイミング設定端子。                                |  |

|                |               |     | [5-1-6 参照]                                                       |  |

|                |               |     | to remain                                                        |  |

表 2-2 MD8405 端子表 (2)

| ピン番号  | ピン名       | I/O | 機能                                        |

|-------|-----------|-----|-------------------------------------------|

| 69    | En_Accel  | I   | PHY レジスタアドレス 5 の Enab_accel ビットのハードウエアリ   |

|       |           |     | セット初期値としてこの端子の状態を反映。                      |

|       |           |     | [3-2-6 Bit 6 参照 ]                         |

| 70    | En_Multi  | I   | PHY レジスタアドレス 5 の Enab_multi ビットのハードウエアリ   |

|       |           |     | セット初期値としてこの端子の状態を反映。                      |

|       |           |     | [3-2-6 Bit 7 参照 ]                         |

| 73    | AVDD2     | -   | アナログ電源 2。                                 |

|       |           |     | ケーブルインターフェイスドライバ用電源。                      |

| 75,76 | TEST[1:0] | I   | テストモード制御端子。通常は DVDD に接続する。                |

| 77    | DIRECT    | 1   | PHY-Link インターフェイス動作モード設定端子。               |

|       |           |     | "L":AC 接続                                 |

|       |           |     | "H":DC 接続                                 |

|       |           |     | [5-1-5 参照]                                |

| 78    | LinkOn    | 0   | Link-On 信号出力。                             |

|       |           |     | Link-On は 6.144[MHz]、デューティ 50[%] の AC 信号。 |

|       |           |     | [5-1-3 参照]                                |

表 2-3 MD8405 端子表 (3)

# 3 コントロールレジスタ

#### 3-1 レジスタアクセス方法

通常、MD8405 の各レジスタは、Link 層 IC からアクセスをします。詳細な方法は、LREQ の 5-1-4-1 章を参照してください。

#### 3-2 レジスタ内容

#### 3-2-1 Register0

アドレス 00h

| 0 | 1           | 2 | 3 | 4 | 5 | 6 | 7 |

|---|-------------|---|---|---|---|---|---|

|   | Physical_ID |   |   |   |   |   |   |

#### Bit 0~5 Physical ID: Physical Node ID(R-初期值:00h)

Self-ID 期間に決定されたこのノードの ID を示します。

このビットはバスリセットで初期化され Self-ID 期間 Self-ID パケット送信時に決定されます。 このビットを含むレジスタアドレス "00h" は Self-ID パケット送信後、ステータス送信として 自動的に Link インターフェイスに出力されます。

#### Bit 6 R: root indicator (R-初期值:0h)

'1' の場合、このノードがルートに設定されていることを示します。 このビットはバスリセットで初期化され Tree-ID 期間に決定されます。

# Bit 7 PS: Cable Power Status (R - 初期値: CPS 端子設定)

CPS 端子の値が反映され、ケーブルからの電源の状態を示します。'1' でケーブルから電源が供給されている事を示します。

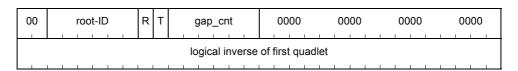

#### 3-2-2 Register1

アドレス 01h

| 0   | 1   | 2 | 3 | 4    | 5     | 6 | 7 |

|-----|-----|---|---|------|-------|---|---|

| RHB | IBR |   |   | Gap_ | count |   |   |

#### Bit 0 RHB: Root Hold Bit (R/W - 初期値: 0h)

'1' の場合、このノードが次のバスリセットで root になるように要求します。 このビットはまた、PHY configuration パケット送受信により自動的に設定されます。

####

このビットを '1' に設定するとすぐにバスリセットを開始します。 このビットはバスリセットにより初期化されます。

#### Bit 2~7 Gap\_Count : Gap Count (R/W - 初期値:3Fh)

Gap Count 值。

このビットは PHY Configuration パケット送受信によっても自動的に設定されます。 このビットは設定後に起こる最初のバスリセットでは値を保持していますがその次のバスリセットにより初期化されます。

#### 3-2-3 Register2

アドレス 02h

| 0 | 1        | 2 | 3 | 4 | 5      | 6      | 7 |

|---|----------|---|---|---|--------|--------|---|

|   | Extended |   |   |   | Total_ | _ports |   |

Bit 0~2 Extended:(R-初期值:111b)

MD8405 がサポートするレジスタマップ、'111b' が読まれます。

**Bit 3 Reserved**:(R-初期値:0h)

通常は0('00b')が読まれます。

Bit 4~7 Total\_ports: Total of Port (R - 初期値: 3h)

MD8405 が持っているポート数を示します。通常は3('0011')が読まれます。

#### 3-2-4 Register3

アドレス 03h

| 0 | 1         | 2 | 3 | 4 | 5  | 6   | 7 |

|---|-----------|---|---|---|----|-----|---|

|   | Max_speed |   |   |   | De | lay |   |

Bit 0~2 Max\_Speed: Speed(R-初期值:S200="L":2h、S200="H":1h)

MD8405 がサポートする最大転送速度を示します。S200 端子が "L" の場合、2 ('010') が読まれます。S200 端子が "H" の場合、1 ('001') が読まれます。

Bit 3 Reserved:(R-初期值:0h)

通常は0('00b')が読まれます。

Bit 4~7 Delay:(R-初期值:1h)

MD8405 のリピート時 Delay のワーストケース時間を示します。通常は 1 ('0001') が読まれ、MD8405 の最大リピート遅延時間は 164ns です。

#### 3-2-5 Register4

アドレス 04h

| 0           | 1         | 2 | 3      | 4 | 5 | 6           | 7 |

|-------------|-----------|---|--------|---|---|-------------|---|

| Link_active | Contender |   | Jitter |   |   | Power_class |   |

Bit 0 Link\_active: Link active(R/W-初期值:1h)

このビットは Self-ID パケットの L (link\_active) フィールドの値を制御します。

Self-ID パケットの L (Link\_active) フィールドにはこのビットと LPS により検出された Link アクティブ信号の論理積を取った値が反映されます。

このビットはハードウェアリセットにより '1' に初期化されます。

Bit 1 Contender: CMC (R/W - 初期値: CMC 端子設定)

このビットは Self-ID パケットの c ( CONTENDER ) フィールドに反映されます。 その意味は Self-ID パケットの c ( CONTENDER ) フィールドと同様です。 このビットはハードウェアリセットにより CMC に初期化されます。

Bit 2~4 Jitter: Jitter(R-初期值:1h)

MD8405 のリピート時 Delay の最大と最小時間の差を示します。通常 '1' が読まれます。 MD8405 のリピート時のジッタは 40ns です。

Bit 5~7 Power\_class: Power Class (R/W - 初期値:PC 端子設定)

このビットは Self-ID パケットの pwr (POWER\_CLASS) フィールドに反映されます。 その意味は Self-ID パケットの pwr (POWER\_CLASS) フィールドと同様です。 このビットはハードウェアリセットにより PC[0:2] に初期化されます。

bit5: PC0(Pin2) bit6: PC1(Pin1) bit7: PC2(Pin79)

#### 3-2-6 Register5

アドレス 05h

| 0          | 1    | 2    | 3        | 4       | 5          | 6          | 7          |

|------------|------|------|----------|---------|------------|------------|------------|

| Resume_int | ISBR | Loop | Pwr_fail | Timeout | port_event | Enab_accel | Enab_multi |

Bit 0 Resume\_int: Resume interrupt enble (R/W - 初期值:0h)

このビットを '1' に設定するとポートの Resume が起こったときに Port\_event ビットをセットします。

Bit 1 ISBR: Initiate Short (Arbitrated) Bus Reset (R/W - 初期値: 0h)

このビットを '1' に設定するとアービトレーションショートバスリセットを開始します。 このビットはバスリセットにより初期化されます。

Bit 2 Loop: Loop detect (R/W-初期值:0h)

'1' の場合、バスがループになっていることを示します。 このビットはハードウエアリセット又は '1' を書き込むことによってクリアされます。

Bit 3 Pwr\_fail: Cable power failure detect (R/W - 初期値:0h)

'1' の場合、PS ビットが 1 から 0 に変化したことを示します。

このビットはハードウエアリセット又は'1'を書き込むことによってクリアされます。

Bit 4 Timeout: Arbtration state machine timeout (R/W - 初期値:0h)

'1' の場合、このノードが A0:Idle、T0:Tree\_IDStart 以外のあるステートから MAX\_ARB\_STATE\_TIME 時間以上抜けなかったことを示します。

このビットはハードウエアリセット又は'1'を書き込むことによってクリアされます。

Bit 5 Port\_event: Port event detect (R/W - 初期値:0h)

MD8405 は Int\_enable が '1' に設定されている場合、Connected、Bias、Disabled、Fault ビットの変化を検出するとこのビットに '1' をセットします。又、Resume\_int が '1' に設定されている場合、Resume が起こるとこのビットに '1' をセットします。

このビットはハードウエアリセット又は'1'を書き込むことによってクリアされます。

Bit 6 Enab\_accel: Enable arbitration acceleration (R/W - 初期值: En Accel 端子設定)

このビットを '1' に設定すると MD8405 は Ack-acceleration アービトレーション、Fly-by アービトレーションを行います。

このビットを '0' に設定すると MD8405 は acceleration アービトレーションを行いません。 このビットはハードウエアリセットにより初期化されます。

**Bit 7 Enab\_multi**: Enable multi-speed packet concatenation(R/W - 初期値: En\_Multi 端子設定) このビットを '1' に設定すると MD8405 は Concatenated パケット転送リクエストの検出と同時 にそのパケットの転送スピードを検出します。

このビットを '0' に設定すると MD8405 は Concatenated パケット転送を最初のパケットと同じスピードで行います。

このビットはハードウエアリセットにより初期化されます。

#### 3-2-7 Register6

アドレス 06h

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

Bit 0~7 Reserved (R - 初期値:0h)

予約

#### 3-2-8 Register7

アドレス 07h

| 0                  | 0 1 2 Page_select |  | 3 | 4 | 5     | 6      | 7 |

|--------------------|-------------------|--|---|---|-------|--------|---|

| 0 1 2  Page_select |                   |  |   |   | Port_ | select |   |

Bit 0~2 Page\_select (R/W - 初期値:0h)

PHY レジスタのアドレス 1000b から 1111b にどのページをアクセスするかを設定します。

Bit 3 Reserved (R-初期値:0h)

予約

Bit 4~7 Port\_select (R/W - 初期値:0h)

Page\_select ビットが Port Status Page を選択している場合、PHY レジスタのアドレス 1000b から 1111b にどのポートをアクセスするかを設定します。

# 3-3 レジスタ一覧

| Name      | Address | 0           | 1           | 2      | 3        | 4           | 5          | 6          | 7          |

|-----------|---------|-------------|-------------|--------|----------|-------------|------------|------------|------------|

| Register0 | 0000    |             |             | Physic | cal_ID   |             |            | R          | PS         |

| Register1 | 0001    | RHB         | IBR         |        |          | Gap_        | count      |            |            |

| Register2 | 0010    |             | Extended    |        |          | Total_ports |            |            |            |

| Register3 | 0011    |             | Max_speed   |        |          | Delay       |            |            |            |

| Register4 | 0100    | Link_active | Contender   |        | Jitter   | Power_cla   |            |            | i          |

| Register5 | 0101    | Resume_int  | ISBR        | Loop   | Pwr_fail | timeout     | port_event | Enab_accel | Enab_multi |

| Register6 | 0110    |             |             |        |          |             |            |            |            |

| Register7 | 0111    |             | Page_Select |        |          |             | Port_      | Select     |            |

| -         | 1000    |             |             |        | Regi     | ster8       |            |            |            |

| -         | 1001    |             |             |        | Regi     | ster9       |            |            |            |

| -         | 1010    |             |             |        | Regi     | sterA       |            |            |            |

| -         | 1011    |             |             |        | Regi     | sterB       |            |            |            |

| -         | 1100    |             |             |        | Regi     | sterC       |            |            |            |

| -         | 1101    |             |             |        | Regi     | sterD       |            |            |            |

| -         | 1110    |             | RegisterE   |        |          |             |            |            |            |

| -         | 1111    |             |             |        | Regi     | sterF       |            |            |            |

表 3-1 レジスター覧表

#### 3-4 Page\_select=0 (Port Status page)

このレジスタは各ポートの状態を反映します。Port\_select ビットを設定することによりアクセスしたいポートを選択できます。

#### 3-4-1 Register00

アドレス 08h

| 0  | 1   | 2  | 3   | 4     | 5         | 6    | 7        |

|----|-----|----|-----|-------|-----------|------|----------|

| As | tat | Bs | tat | Child | Connected | Bias | Disabled |

#### Bit 0~1 Astat: Status of TPA (R - 初期值: 3h)

TpA の状態を示します。値の意味は下記のとおりです。

'11b': Z '01b': 1 '10b': 0 '00b': invalid

#### Bit 2~3 Bstat: Status of TPB(R-初期值:3h)

TpB の状態を示します。値の意味は下記のとおりです。

'11b': Z '01b': 1 '10b': 0 '00b': invalid

#### Bit 4 Child: Child(R-初期值:0h)

'1' の場合、ポートが Child であることを示します。'0' の場合、ポートが Parent です。このビットはバスリセットで初期化され Tree-ID 期間に決定されます。

#### Bit 5 Connected: Connected(R-初期值:0h)

'1'の場合、MD8405 はポートに対向ノードが接続されていると認識していることを示します。

#### Bit 6 Bias: Cable Bias(R-初期值:0h)

ポートに検出されるケーブルバイアスを反映します。 '1' でポートに TpBias を検出したことを示します。

#### Bit 7 Disabled: Port Disabled (R/W - 初期値: DISABLED)

'1' に設定された場合このポートは Disabled 状態です。 このビットはハードウエアリセットにより初期化されます。

#### 3-4-2 Register01

アドレス 09h

| 0 | 0 1 2          |    | 3          | 4     | 5 | 6 | 7 |

|---|----------------|----|------------|-------|---|---|---|

|   | Negotiated_spe | ed | Int_enable | Fault |   |   |   |

#### Bit 0~1 Negotiated\_speed: Negotiate speed(R-初期值:0h)

ポートに対向して接続されているノードのスピードを示します。 このビットはバスリセットで初期化され Self-ID 期間に決定されます。 値の意味は下記のとおりです。

'000b': 対向ノードの最大転送速度が 100Mbps であることを示します。'001b': 対向ノードの最大転送速度が 200Mbps であることを示します。'010b': 対向ノードの最大転送速度が 400Mbps であることを示します。

'1' が設定された場合、このポートの Connected,Bias,Disabled,Fault ビットが変化したとき、Port event ビットを '1' にセットします。

このビットはハードウエアリセットにより初期化されます。

Bit 3 Fault: (R/W-初期值:0h)

'1' の場合、Suspend/Resume 動作中にエラーが起こった事を示します。 このビットはハードウエアリセット又は '1' を書き込むことによってクリアされます。

Bit 4~7 Reserved:(R-初期值:0h)

予約

#### 3-4-3 Register02

アドレス 0Ah

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

Bit 0~7 Reserved:(R-初期值:0h)

予約

#### 3-4-4 Register03

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

アドレス 0Bh

Bit 0~7 Reserved:(R-初期值:0h)

予約

#### 3-4-5 Register04

アドレス 0Ch

Bit 0~7 Reserved : ( R - 初期値: 0h )

予約

# 3-4-6 Register05

アドレス 0Dh

# 3-4-7 Register06

アドレス 0Eh

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

**Bit 0~7 Reserved**:(R-初期值:0h) 予約

# 3-4-8 Register07

アドレス 0Fh

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

# 3-5 Page\_select=0 一覧

| Name       | Address | 0                | 1   | 2  | 3          | 4     | 5         | 6    | 7        |

|------------|---------|------------------|-----|----|------------|-------|-----------|------|----------|

| Register00 | 1000    | As               | tat | Bs | stat       | Child | Connected | Bias | Disabled |

| Register01 | 1001    | Negotiated_speed |     |    | Int_enable | Fault |           |      |          |

| Register02 | 1010    |                  |     |    |            |       |           |      |          |

| Register03 | 1011    |                  |     |    |            |       |           |      |          |

| Register04 | 1100    |                  |     |    |            |       |           |      |          |

| Register05 | 1101    |                  |     |    |            |       |           |      |          |

| Register06 | 1110    |                  |     |    |            |       |           |      |          |

| Register07 | 1111    |                  |     |    |            |       |           |      |          |

表 3-2 page\_select=0 一覧表

#### 3-6 Page\_select=1 (Vendor Identification page)

#### 3-6-1 Register10

アドレス 08h

| 0 | 1 | 2 | 3        | 4         | 5 | 6 | 7 |

|---|---|---|----------|-----------|---|---|---|

|   |   |   | Compliar | nce_level |   |   |   |

**Bit 0~7 Compliance\_level**:(R-初期値:1h) 通常'1'が読まれます。

#### 3-6-2 Register11

アドレス 09h

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

Bit 0~7 Resrved:(R-初期値:0h) 予約

#### 3-6-3 Register12

アドレス 0Ah

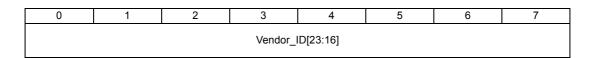

**Bit 0~7 Vendor\_ID[23:16]**:(R-初期値:00h) 通常'00h' が読まれます。

#### 3-6-4 Register13

アドレス 0Bh

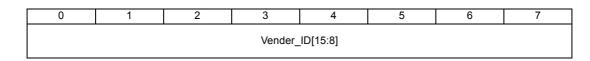

**Bit 0~7 Vender\_ID[15:8]**:(R-初期値:C0h) 通常'C0h' が読まれます。

#### 3-6-5 Register14

アドレス 0Ch

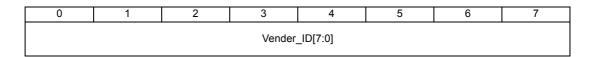

**Bit 0~7 Vender\_ID[7:0]**:(R-初期値:2Dh) 通常'2Dh' が読まれます。

#### 3-6-6 Register15

アドレス 0Dh

| 0 | 1 | 2 | 3        | 4          | 5 | 6 | 7 |

|---|---|---|----------|------------|---|---|---|

|   |   |   | Product_ | [ID[23:16] |   |   |   |

**Bit 0~7 Product\_ID[23:16]**:(R-初期値:30h) 通常'30h'が読まれます。

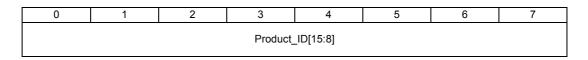

#### 3-6-7 Register16

アドレス 0Eh

**Bit 0~7 Product\_ID[15:8]**:(R-初期値:35h) 通常'35h' が読まれます。

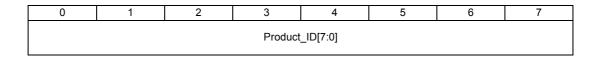

#### 3-6-8 Register17

アドレス 0Fh

**Bit 0~7 Product\_ID[7:0]**:(R-初期値:65h) 通常'65h'が読まれます。

# 3-7 Page\_select=1 一覧

| Name       | Address | 0 | 1                | 2 | 3        | 4         | 5 | 6 | 7 |  |  |

|------------|---------|---|------------------|---|----------|-----------|---|---|---|--|--|

| Register10 | 1000    |   |                  |   | Compliar | nce_level |   |   |   |  |  |

| Register11 | 1001    |   |                  |   |          |           |   |   |   |  |  |

| Register12 | 1010    |   |                  |   | Vendor_  | ID[23:16] |   |   |   |  |  |

| Register13 | 1011    |   | Vender_ID[15:8]  |   |          |           |   |   |   |  |  |

| Register14 | 1100    |   | Vender_ID[7:0]   |   |          |           |   |   |   |  |  |

| Register15 | 1101    |   |                  |   | Product_ | ID[23:16] |   |   |   |  |  |

| Register16 | 1110    |   | Product_ID[15:8] |   |          |           |   |   |   |  |  |

| Register17 | 1111    | _ | Product_ID[7:0]  |   |          |           |   |   |   |  |  |

表 3-3 page\_select=1 一覧表

#### 3-8 Page\_select=7 (Vendor Dependent page)

#### 3-8-1 Register70

アドレス 08h

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

Bit 0~7 Reserved:(R-初期值:0h)

予約

#### 3-8-2 Register71

アドレス 09h

| 0       | 1 | 2 | 3 | 4 | 5 | 6 | 7    |

|---------|---|---|---|---|---|---|------|

| LPSISBR |   |   |   |   |   |   | EnDV |

'1'を設定することにより LPS ディセーブル後 ISBR をセットします。

Power\_class、Contender ビットを PC、C に初期化し、RHB ビットをクリアします。

Bit 1~6 Reserved:(R-初期值:0h)

予約

**Bit7 EnDV**:(R/W-初期值:1h)

'1' にセットすることにより、BIAS HANDSHAKE TIME を変更します。

'0' の場合は P1394a Draft Ver2.0 規格で動作します。

ハードウェアリセット後は初期化されます。

SR 端子 ="L" の時はこのビットは無効です。

#### 3-8-3 Register72

アドレス 0Ah

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

Bit 0~7 Reserved:(R-初期值:0h)

予約

#### 3-8-4 Register73

アドレス 0Bh

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|---|

| I |   |   |   |   |   |   |   |   |

| ١ |   |   |   |   |   |   |   |   |

# 3-8-5 Register74

アドレス 0Ch

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

#### 3-8-6 Register75

アドレス 0Dh

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

# 3-8-7 Register76

アドレス 0Eh

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

**Bit 0~7 Reserved**:(R-初期值:0h) 予約

# 3-8-8 Register77

アドレス 0Fh

|     | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|-----|---|---|---|---|---|---|---|---|

|     |   |   |   |   |   |   |   |   |

| - 1 |   |   |   |   |   |   |   |   |

20

# 3-9 Page\_select=7 一覧

| Name       | Address | 0       | 1 | 2 | 3 | 4 | 5 | 6 | 7    |

|------------|---------|---------|---|---|---|---|---|---|------|

| Register70 | 1000    |         |   |   |   |   |   |   |      |

| Register71 | 1001    | LPSISBR |   |   |   |   |   |   | EnDV |

| Register72 | 1010    |         |   |   |   |   |   |   |      |

| Register73 | 1011    |         |   |   |   |   |   |   |      |

| Register74 | 1100    |         |   |   |   |   |   |   |      |

| Register75 | 1101    |         |   |   |   |   |   |   |      |

| Register76 | 1110    |         |   |   |   |   |   |   |      |

| Register77 | 1111    |         |   |   |   |   |   |   |      |

表 3-4 page\_select=7 一覧表

# 4 データフォーマット

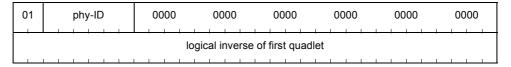

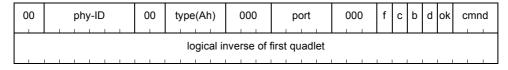

#### 4-1 Self-ID Packet

MD8405 が送信する Self-ID はパケット 2quadlet で、図 4-1 に示すフォーマットに従います。 MD8405 はバス初期化の Self-ID 期間に、以下の Self-ID パケットを送信します。 また、MD8405 は Ping パケットを受信するとそのレスポンスとして自動的に Self-ID パケットを送信します。

| 0 1 | 2 3 4 5 6                        | 7 8 9 | 10 11 12 13 14 15 | 16 17 | 18 19 20 | 21 22 23 | 24 25 | 26 27 | 28 29 | 30 31 |  |

|-----|----------------------------------|-------|-------------------|-------|----------|----------|-------|-------|-------|-------|--|

| 10  | 10 phy-ID 0 L gap_cnt            |       | sp                | rsv c | pwr      | p0       | p1    | p2    | i m   |       |  |

|     | logical inverse of first quadlet |       |                   |       |          |          |       |       |       |       |  |

図 4-1 Self-ID パケットフォーマット

phy\_ID : physical\_ID フィールド

自分自身の physical\_ID。

L : Link active フィールド

Self-ID パケット送信時の LPS 端子の論理値と PHYRegister4 の Link\_active ビットの論理積が反映されます。

gap\_cnt : gap count フィールド

PHY Register1 Gap Count の値が反映されます。

sp : PHY\_SPEED フィールド

00 = 98.304Mbps

01 = 98.304 **\( \Leq \)** 196.608Mbps

10 = 98.304 ≥ 196.608 ≥ 393.216Mbps

11 = 予約

使用可能なスピードが格納されます。MD8405 では、10 固定です。S200 端子が "L" の場合 10、S200 端子が "H" の場合 01 です。

rsv : 00 固定です。

C : CONTENDER フィールド

PHYRegister4 の Contender ビットの値が反映されます。

pwr : POWER CLASS フィールド

bit21 = PC0(Pin2) bit22 = PC1(Pin1)

bit23 = PC2(Pin79)

PHYRegister4 の Pwr ビットが反映されます。IEEEP1394a Draft Ver2.0 では以下のように定義されています。

000 = ノードは電源を必要としません。ノードは電源をリピートしません。

001 = ノードは電源を自分自身で持ち、最小 15W を供給できます。

010 = ノードは電源を自分自身で持ち、最小 30W を供給できます。

011 = ノードは電源を自分自身で持ち、最小 45W を供給できます。

100 = ノードはケーブルから電源を最大でも 3W まで消費します。しかし、Link やそれより上位の層をイネーブルするために電力を消費しません。

101 = 予約。

110 = ノードはケーブルから電源を最大でも 3W まで消費します。さらに、Link やそれより上位の層をイネーブルにするために 3W まで消費します。

111 = ノードはケーブルから電源を最大でも 3W まで消費します。さらに、Link やそれより上位の層をイネーブルにするために 7W まで消費します。

**p0 ... p2** : Port status フィールド

11 = Active でかつ child ノードに接続されています。

10 = Active でかつ parent ノードに接続されています。

01 = Active ではありません。(disabled,disconnected,suspended)

00 = この PHY は提供していません。

ポートのステータスを示します。

i : initiated reset フィールド

今回、このノードが BusReset を発行したことを示します。

m : more\_packets フィールド

複数の Self-ID パケットを送信する場合、このフィールドは 1 にセットされますが、MD8405では 0 固定です。

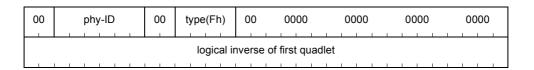

#### 4-2 Link-on Packet

図 4-2 Link-on パケットフォーマット

#### 4-3 PHY Configuration Packet

図 4-3 PHY Configuration パケットフォーマット

#### 4-4 Extended PHY Packet

#### 4-4-1 Ping Packet

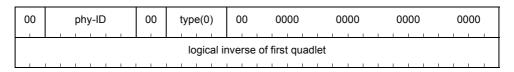

図 4-4 Ping パケットフォーマット

#### 4-4-2 Remote Access Packet

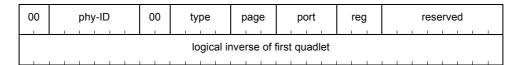

図 4-5 Remote Access パケットフォーマット

#### 4-4-3 Remote Reply Packet

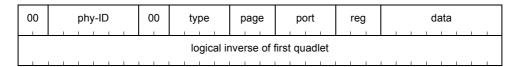

図 4-6 Remote Reply パケットフォーマット

#### 4-4-4 Remote Command Packet

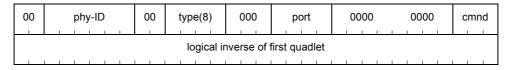

図 4-7 Remote Command パケットフォーマット

#### 4-4-5 Remote Confirmation Packet

図 4-8 Remote Confirmation パケットフォーマット

#### 4-4-6 Resume Packet

図 4-9 Resume パケットフォーマット

# 5 機能説明

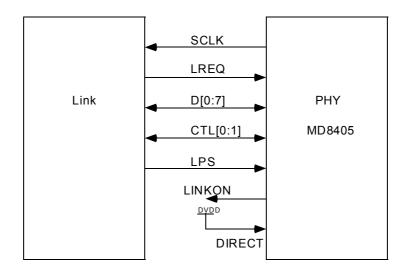

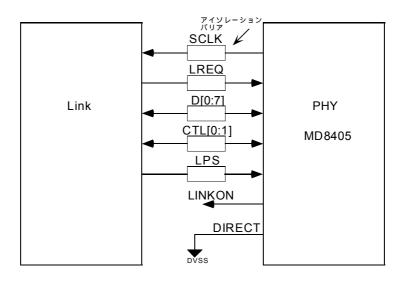

## 5-1 Link チップインターフェイス

# 5-1-1 接続方法

#### 5-1-1-1 DC 接続

図 5-1 MD8405 と Link チップの接続図 (DC 接続)

## 5-1-1-2 AC 接続

図 5-2 MD8405 と Link チップの接続図 (AC 接続)

#### 5-1-2 LPS(Link Power Status)

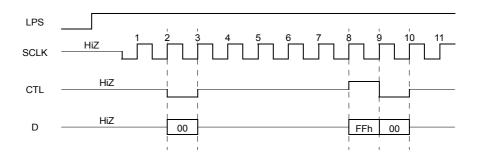

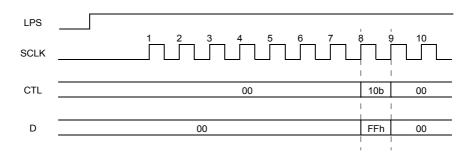

LPS 端子への入力により MD8405 は PHY/Link インターフェイスをイネーブル / ディセーブルします。

MD8405 は LPS 端子が  $T_{LPS\_RESET}$  期間論理的にデアサートであると認識すると PHY/Link インターフェイスをリセットします。 PHY/Link インターフェイスが DC 接続の場合、 MD8405 は Ctl[0:1],D[0:7] に 0 を出力します。 AC 接続の場合は Hi-Z 状態にします。

さらに MD8405 は LPS 端子が  $T_{LPS\_DISABLE}$  期間論理的にデアサートであると認識すると PHY/Link インターフェイスをディセーブルします。 PHY/Link インターフェイスが DC 接続の場合、MD8405 は SCLK,Ctl[0:1],D[0:7] に 0 を出力します。 AC 接続の場合は Hi-Z 状態にします。

PHY/Link インターフェイスがリセットされた場合すべてのバスリクエスト、レジスタリードリクエストはキャンセルされます。

Link がパケット転送中に PHY/Link インターフェイスがリセットされた場合 MD8405 はパケット転送が終了したと認識し動作します。

PHY/Link インターフェイスをディセーブルしている期間のステータス出力は行われません。また、この情報は PHY/Link インターフェイスをイネーブルした後も出力されません。

PHY/Link インターフェイスがリセット / ディセーブル後 MD8405 は LPS がアサートされたことを検出するとディセーブル後はSCLKの出力を開始します。PHY/LinkインターフェイスがDC接続の場合、MD8405 は LPS の検出後 7SCLK サイクル Ctl,D に 0 を出力し、8SCLK 目に PHY/Link インターフェイスに Data\_Prefixの Receive(Ctl[0:1]=10b,D[0:7]=ffh) を出力し通常動作に戻ります。 AC 接続の場合、LPS の検出後 1 から 6SCLK サイクル内の 1SCLK サイクル期間 Ctl,D に 0 を出力し、8SCLK サイクル目に PHY/Link インターフェイスに Data\_Prefixの Receive(Ctl[0:1]=10b,D[0:7]=ffh) を出力し通常動作に戻ります。それ以外の期間は Hi-Z 状態です。

この時このノードがパケット受信中であるとパケット受信が終了するまで PHY/Link インターフェイス に Data Prefix の Receive を出力し続けます。

図 5-3 AC 接続時の LPS 波形

| 記号           | 項目                                | 単位 | MIN  | MAX  |

|--------------|-----------------------------------|----|------|------|

| TLPSL        | LPS low 時間 (パルス時 )                |    | 0.09 | 1.00 |

| TLPSH        | LPS high 時間 (パルス時 )               |    | 0.09 | 1.00 |

| TLPS_RESET   | MD8405 が、LPS を論理的にデアサートだと認識し、PHY/ |    | 1.2  | 27   |

|              | Link インターフェイスをリセットする時間            | μs | 1.2  | 2.1  |

| TLPS_DISABLE | MD8405 が、LPS を論理的にデアサートだと認識し、PHY/ |    | 25   | 20   |

|              | Link インターフェイスをディセーブルする時間          | μs | 25   | 30   |

表 5-1 LPS タイミング

#### 5-1-3 LinkOn

MD8405 は LPS が論理的にデアサートであると認識するか、PHY レジスタの Link\_active ビットが 0 である場合に Link が非アクティブであると認識します。

通常 LinkOn は "L" を出力していますが、MD8405 が Link が非アクティブであると認識している間にこのノード宛の LinkOn パケットを受信すると LinkOn の信号を出力します。

また、この間に PHY レジスタの Loop ビット、Pwr\_fail ビット、Timeout ビット、Port\_event ビットが 1 に変化した場合は Interrupt 出力として LinkOn 信号を出力します。

LinkOn 信号は Link が非アクティブである期間出力され続けます。その後、Link がアクティブになると LinkOn は "L" を出力します。

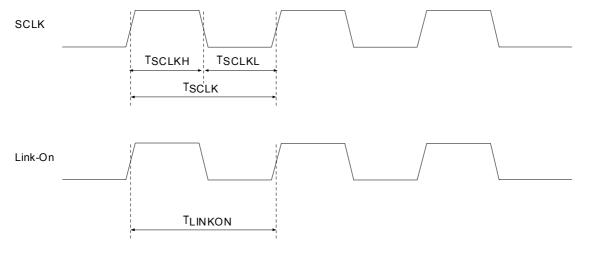

LinkOn 信号は周波数 6.144MHz、デューティー 50% の AC 信号です。

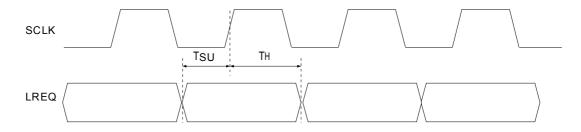

#### 5-1-4 Link インターフェイス (LREQ、CTL[0:1]、D[0:7])

MD8405 の PHY-Link インターフェイスは IEEEP1394a Draft Ver2.0 に準拠しています。

PHY-Link インターフェイスでは LREQ によるリクエスト、また CTL によるステータス送信、パケット 転送、パケット受信の 4 つの動作があります。リクエスト以外の CTL を使う動作はまず PHY により制御 されます。

MD8405 はパケットを受信すると優先的にパケット受信動作を開始します。

表 5-2、表 5-3 に CTL の状態とその意味を示します。

| CTL[0:1] | 動作      | 内容                            |  |

|----------|---------|-------------------------------|--|

| 00b      | Idle    | 可も動作していないアイドル状態 (デフォルトモード)    |  |

| 01b      | Status  | ステータス情報の転送を行う                 |  |

| 10b      | Receive | 受信パケット内容の転送を行う                |  |

| 11b      | Grant   | 『ケット転送するために PHY-Link インターフェイス |  |

|          |         | を Link に与える                   |  |

表 5-2 PHY が CTL を制御する動作

上記 Grant 後 Link が PHY-Link のバスをコントロールできるようになった後は表 5-3 に示す動作モードになります。

| CTL[0:1] | 動作       | 内容                                |

|----------|----------|-----------------------------------|

| 00b      | Idle     | パケット転送を完了。PHY-Link インターフェイスを開放する。 |

| 01b      | Hold     | ・転送パケットデータが確定するまで PHY-Link インター   |

|          |          | フェイスをホールドしている。                    |

|          |          | ・Concatenated パケット転送を要求する         |

| 10b      | Transmit | PHY に転送パケットのデータを入力している。           |

| 11b      | Reserved | 予約                                |

表 5-3 Link が CTL を制御する動作

#### 5-1-4-1 LREQ

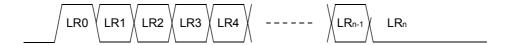

パケット送信、PHY レジスタのアクセスまたは、アクセラレーションコントロールを要求するために、Link チップは LREQ 端子に SCLK に同期したシリアル信号を入力します。このシリアル信号にはリクエストタイプ、転送するパケットの速度、読み出し / 書き込みコマンドの情報が含まれます。

LREQ シリアル信号の長さはその要求のタイプにより異なり、アクセラレーションコントロールリクエストでは 6 ビット、バスリクエストでは 7 ビット、レジスタリードリクエストでは 9 ビット、レジスタライトリクエストでは 17 ビットとなります。

このシリアル信号は最後にストップビットとして '0' を送信する必要があります。

LRn=LREQn

図 5-4 LREQ ストリーム

パケット転送要求は表 5-4 に示す 7 ビット長のフォーマットにて行われます。

| Bit(s) | タイプ           | 内容                     |

|--------|---------------|------------------------|

| 0      | Start Bit     | 転送開始を示す。いつも '1' を転送する。 |

| 1~3    | Request Type  | 表 5-9 に示す要求のタイプを示す。    |

| 4~5    | Request Speed | 転送するパケットの速度を示す。        |

| 6      | Stop Bit      | 転送完了を示す。いつも '0' を転送する。 |

表 5-4 Request フォーマット

| Data Rate |

|-----------|

| 100Mbps   |

| 200Mbps   |

| 400Mbps   |

| Reserved  |

|           |

表 5-5 Speed フォーマット

PHY チップのレジスタ読み出しの要求は表 5-6 に示す 9 ビット長のフォーマットにて行われます。また、レジスタ書き込み要求は表 5-7 に示す 17 ビット長のフォーマットにて行われます。

| Bit(s) | タイプ          | 内容                      |

|--------|--------------|-------------------------|

| 0      | Start Bit    | 転送開始を示す。いつも '1' を転送する。  |

| 1~3    | Request Type | 表 5-9 に示す要求のタイプを示す。     |

| 4~7    | Address      | 読み出す PHY のレジスタのアドレスを示す。 |

| 8      | Stop Bit     | 転送完了を示す。いつも '0' を転送する。  |

表 5-6 Read Register フォーマット

| Bit(s) | タイプ          | 内容                      |

|--------|--------------|-------------------------|

| 0      | Start Bit    | 転送開始を示す。いつも '1' を転送する。  |

| 1~3    | Request Type | 表 5-9 に示す要求のタイプを示す。     |

| 4~7    | Address      | 書き込む PHY のレジスタのアドレスを示す。 |

| 8~15   | Data         | 書き込む PHY のレジスタのデータを示す。  |

| 16     | Stop         | 転送完了を示す。いつも '0' を転送する。  |

表 5-7 Write Register フォーマット

アクセラレーションコントロール要求は表 5-8 に示す 6 ビット長のフォーマットにて行われます。

|        |              | •                             |

|--------|--------------|-------------------------------|

| Bit(s) | タイプ          | 内容                            |

| 0      | Start Bit    | 転送開始を示す。いつも '1' を転送する。        |

| 1~3    | Request Type | 表 5-9 に示す要求のタイプを示す。           |

| 4      | Accelerate   | '0' の時、アービトレーションアクセラレーションをディ  |

|        |              | セーブルすることを示す。                  |

|        |              | '1' の時、アービトレーションアクセラレーションをイネー |

|        |              | ブルすることを示す。                    |

| 5      | Stop Bit     | 転送完了を示す。いつも '0' を転送する。        |

表 5-8 アクセラレーションコントロールフォーマット

| LREQ[1:3] | タイプ      | 内容                      |

|-----------|----------|-------------------------|

| 000       | ImmReq   | イミディエート要求               |

| 001       | IsoReq   | Isochronous 要求          |

| 010       | PriReq   | プライオリティ要求               |

| 011       | FairReq  | フェア要求                   |

| 100       | RdReg    | 設定したレジスタの内容を読み出し        |

| 101       | WrReg    | 設定したレジスタに書き込み           |

| 110       | AccCtrl  | PHY アービトレーションアクセラレーションを |

|           |          | ディセーブル / イネーブルする。       |

| 111       | Reserved | Reserved                |

表 5-9 Request Type

フェアリクエスト及びプライオリティリクエストは CTL が Idle になってから少なくとも 1SCLK 以降から LREQ の発行を開始しなければなりません。Link がこれらのリクエストを発行中または発行後に CTL が Receive となった場合、MD8405 はこのリクエストをキャンセルします。 そのため Link は次に CTL が idle になった時に再度このリクエストを発行する必要があります。

但し、PHYRegister5の Enab\_accel ビットが'1'に設定され、アクセラレーションアービトレーション (Ack-Acceleration アービトレーション、Fly-By アービトレーション) がイネーブルとなっている時でかつ、受信

パケットが Ack パケット (8 ビット長のパケット) であった場合は、そのリクエストはこの Receive によりキャンセルされません。

サイクルマスターの Link はサイクルスタートパケットを転送するために PriReq を発行します。

アイソクロナスパケットを送信するために Link は IsoReq を発行します。 IsoReq はサイクルスタートパケット、もしくはアイソクロナスパケットの送信中および送信後 8SCLK サイクル以内か受信中および受信後 4SCLK サイクル以内に発行しなければなりません。

MD8405 は IsoReq を、アービトレーションに勝ち Link に Grant を送信したとき、サブアクションギャップを検出したとき、またはバスリセットが起こったときにのみクリアします。

Ack パケットを送信するために Link はパケット受信中および受信後 4SCLK サイクル以内に ImmReq を 発行します。ACK\_RESPONSE\_TIME を満足するために、Link は受信パケットの destination\_ID を確認し、このノード宛のパケットであることを確認したらすぐに ImmReq を発行しなければなりません。MD8405 は パケット受信終了後すぐにバスを取得し Link に Grant を返します。もし Link が CRC エラーを発見した場合は Link はその Grant にデータを返さずに、そのリクエストをキャンセルしなければいけません。(5-1-4-3 Transmit 参照)

レジスタライトリクエストの受信が完了するとすぐに MD8405 はそのアドレスのデータを書き換えます。

レジスタリードリクエストを受信すると MD8405 はそのアドレスのデータをステータス送信としてLink に出力します。もしパケット受信 / 送信によりその出力が中断された場合は MD8405 はそのステータス出力が完全に終了するまで再び最初のビットからステータス出力を繰り返します。

MD8405 は 1 つのバスリクエスト(FairReq,PriReq,IsoReq,ImmReq)を受信するとそのリクエストがパケット受信、パケット送信、サブアクションギャップ (IsoReq,ImmReq の場合のみ)等によりキャンセルされるまで次のバスリクエストを無視します。

MD8405 はレジスタリードリクエストが完了する前に次のレジスタリードリクエストを受信した場合、その動作は不定となります。

ずべてのバスリクエストはバスリセットによりクリアされます。

PHYRegister5 の Enab\_accel ビットが '1' に設定されアクセラレーションアービトレーション (Ack-Accelerationアービトレーション、Fly-Byアービトレーション )がイネーブルとなっている場合にも、MD8405 はアクセラレーションコントロールリクエストにより、Accelerating ビットが '0' の期間、アシンクロナスパケットのアクセラレーションアービトレーションをディセーブルします。

MD8405 は IsoReg によっても自動的に Accelerating ビットをセットし、アクセラレーションアービトレーションをイネーブルします。

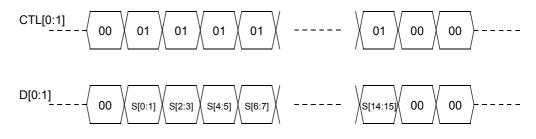

#### 5-1-4-2 Status 出力

MD8405 は表5-10で示される情報をステータス出力としてLinkインターフェイスに出力します。MD8405 は CTL 端子に '01b' をアサートし D[0:1] 端子に情報を出力します。ステータス出力を行っている期間 CTL 端子は '01b' を出力します。

MD8405 は通常はステータス出力として Link ステートマシンで必要な最初の 4 ビットのみを出力します (Arbitration Reset Gap, Subaction Gap, Bus Reset, PHY interrupt)。

しかし、Link からレジスタリードリクエストを受信したときにはその戻り値として、全てのステータス情報を出力します。また、MD8405 は Self-ID 期間に自分の Self-ID パケットを送信し終わった時点 (自分の physical\_ID が確定した時点)で Link に対して自分の physical\_ID を含むアドレス '00h' の PHY レジスタ情報を自動的にステータス出力します。

ステータス出力は、パケットの受信 / 送信等により中断される場合があります。ステータス出力が中断された場合は、次のルールにしたがってそのステータス情報を繰り返し出力します。

- 中断される前に出力し終わった情報はクリアされステータス出力は繰り返されません。

- ステータス出力は S[0:1] ビットから開始され 4 ビット /16 ビット単位で行われます。

図 5-5 Status

| Bit(s) | タイプ                   | 内容                        |

|--------|-----------------------|---------------------------|

| 0      | Arbitration Reset Gap | Arbitration Reset Gap を検出 |

| 1      | Subaction Gap         | Subaction Gap を検出         |

| 2      | Bus Reset             | Bus Reset を検出             |

| 3      | PHY Interrupt         | ホストへ割込みを要求                |

| 4~7    | Address               | ステータスを返す PHY レジスタのアドレス    |

| 8~15   | Data                  | ステータスデータ                  |

表 5-10 Status フォーマット

MD8405 は Phy interrupt として次の場合にステータス出力します。

- バスの構成がループになっている事を検出したとき

- ケーブル電圧が低下したことを検出したとき

- MD8405 のステートマシンがタイムアウトしたとき

- Port event ビットが '1' に変化したとき

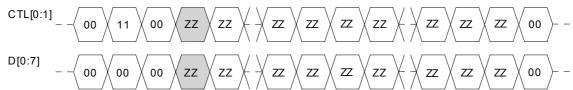

#### 5-1-4-3 Transmit

Link からのバスリクエストを受信すると MD8405 はアービトレーションを行います。そのアービトレーションに勝てば MD8405 は Link に対して Grant として CTL 端子に 1SCLK サイクル Grant( '11b' )と 1SCLK サイクル Idle を返し、CTL、D の制御を Link に与えます。

その後 Link は CTL に Transmit ('10b') かもしくは Hold ('01b') を入力し PHY-Link インターフェイスを制御します。但し、MD8405 は CTL バスでのデータの衝突を防ぐために、Link がその前に 1SCLK だけ Idle ('00b') を入力することを許可しています。(図 5-6 参照)

Link は転送データが準備出来るまでの時間 CTL に Hold('01b') を入力しバスの使用を維持出来ますが、MAX\_HOLD 時間を超えてはいけません。その後 CTL に Transmit ('10b') を入力し転送データの有効範囲を示します。

#### Single Packet

#### **PHY Drive**

#### **Link Drive**

#### Concatenated Packet

#### **PHY Drive**

#### Link Drive

図 5-6 Transmit

パケットデータの最後のビットを入力し終わった後 Link は 1SCLK サイクル Idle ('00b') か Hold ('01b') を入力しその後 1SCLK サイクル Idle を入力します。その後は MD8405 が PHY-Link インターフェイスの制御を行います。

この Hold('01b') ビットは、Link がパケット転送を終了した後、シリアルバスを手放す事なく次のパケットを転送するために使用されます(Concatenated Packet)。MD8405 はこの Hold ビットを検出すると MIN\_PACKET\_SEPARATION 時間後に再び Link に対して CTL 端子に Transmit を出力します。その後 Link は同様にパケット転送動作を行います。

この Hold 動作は Ack パケット送信後にレスポンスパケットを転送する場合と、同一のアイソクロナスサイクル期間に複数のアイソクロナスパケットを転送する場合に使用されます (Subaction concatenation)

Concatenated パケット転送を行う場合、MD8405 は PHYRegister5 の Enab\_multi ビットの設定により Concatenated パケットの転送スピードを決定します。

Enab\_multi ビットが '0' に設定されている場合は MD8405 は、2 つ目以降のパケットスピードは最初のパケットスピードと同じであると認識します。

反対に Enab\_multi ビットが '1' に設定されている場合は MD8405 は、その Concatenated パケットの転送 スピードは CTL に Hold('01b') を入力されている時に D に入力される SP の値により認識します。この SP の値の意味は表 5-11 に示します。

但し、IEEE1394 では Concatenated パケット転送する場合に転送スピードに関する制限が有り、S200 以上で転送されるパケットの後に S100 転送のパケットを Concatenated パケットとして送信することが出来ません。

MD8405 はこのスピード制限を守るために、200Mbps 以上のパケット転送要求が有った後に 100Mbps Concatenated パケット転送要求を受信した場合は、その 100Mbps パケットを Single パケットとして送信しようとする為、一度 1394 バスを手放し、再度アービトレーションを行います。そのために Link からのこの 100Mbps Concatenate パケット転送要求は通常の LREQ で入力されるバスリクエストと同様に扱われ、Grant 以外の CTL を返す場合 (リクエストがキャンセルされる場合)が有ります。

パケットの転送をキャンセルするには次の2つの方法があります。

Link が PHY / Link インターフェイスの制御を得た後、3SCLK サイクル Idle ('00b') を入力し、PHY / Link インターフェイスを手放すか、Link が Hold ('01b') を入力し、バスを維持した後に 2SCLK サイクル Idle を入力し、PHY / Link インターフェイスを手放します。

この時、シリアルバスには空パケットが出力されます。

#### 5-1-4-4 Receive

MD8405 がパケットを受信すると Link に対して CTL 端子を Receive('10b'), D 端子には '1' を出力します。その後 MD8405 はスピードコード (SP) を出力しパケットデータの出力を開始します。MD8405 はデータ受信が終了するまで CTL 端子には Receive('10b') をアサートし続けます。その後 MD8405 は Idle('00b') をアサートし、パケットの受信が終了したことを示します。

MD8405 はまた、Self-ID 期間に自分の送信する Self-ID パケットを Link インタフェースに Receive 動作として出力します。

MD8405 はまた、このノードあての Extended PHY パケットに対するレスポンスパケットも Link インターフェイスに Receive 動作として出力します。

MD8405 は Receive をアサートした後、パケットデータを出力せずに受信動作を終了する場合があります。

Link が 100Mbps しかサポートしていない場合はスピードコード (SP) を確認し、200Mbps、400Mbps の受信パケットデータを無視する必要があります。

Link が 100/200Mbps しかサポートしていない場合はスピードコード (SP) を確認し、400Mbps の受信パケットデータを無視する必要があります。

#### **PHY Drive**

図 5-7 Receive

| D[0:7]    | Data Rate |

|-----------|-----------|

| 00XXXXXXb | 100Mbps   |

| 0100XXXXb | 200Mbps   |

| 01010000b | 400Mbps   |

表 5-11 スピードコード (SP[0:7])

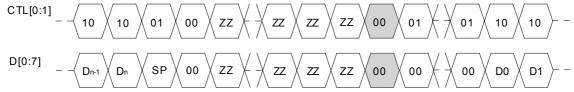

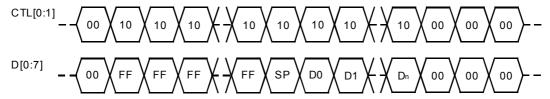

#### 5-1-4-5 Link インターフェイス初期化動作

MD8405 は P1394a Draft Ver2.0 で規定されている PHY/Link インターフェイスの初期化動作を行います。 初期化は LPS がアサートされた後の SCLK クロックに従って以下の様に行われます。

| インターフェイスモード (DIRECT)                    |                                          |  |

|-----------------------------------------|------------------------------------------|--|

| AC 接続 (DIRECT="L")                      | DC 接続 (DIRECT="H")                       |  |

| LPS がアサートされ、その後 SCLK が出力される。そ           | LPS がアサートされ、その後 SCLK が出力される。そ            |  |

| の SCLK の 2 クロック目で CTL[0:1]、D[0:7] に 1 ク | の SCLK の 7 クロック目まで CTL[0:1]、D[0:7] に "0" |  |

| ロック分だけ "0" をドライブ、それ以外は Hiz。             | をドライブ、8 クロック目に CTL[0:1]="10b"、           |  |

| その後 8 クロック目に CTL[0:1]="10b" をドライブ、      | D[0:7]="FFh" をドライブ。                      |  |

| D[0:7] は "FFh" をドライブします。                |                                          |  |

表 5-12 Link インターフェイス初期化動作

図 5-8 AC 接続時の PHY/Link インターフェイス初期化

図 5-9 DC 接続時の PHY/Link インターフェイス初期化

#### **5-1-5 DIRECT**

この端子には PHY-Link インターフェイスの接続情報を入力します。

PHY-Link インターフェイスが DC 接続されている場合はこの端子を "H" に設定します。

PHY-Link インターフェイスが AC 接続されている場合はこの端子を "L" に設定します。

この端子が "L" に設定されている場合、MD8405 は PHY-Link インターフェイスにアイソレーションバリアが存在すると認識し、CTL、D 信号に論理微分波形を出力します。

(詳細は5-1-7 アイソレーションバリアの章を参照してください。)

#### 5-1-6 LDSEL

この端子により PHY-Link インターフェイス AC タイミングを設定します。

この端子の設定により、接続する Link の出力遅延時間、アイソレーションバリアの遅延時間を考慮して MD8405 の入力セットアップ / ホールド時間を切り替えることが出来ます。

この端子による PHY-Link インタフェースの AC タイミングを表 6-5 に示します。

#### 5-1-7 アイソレーションバリア

DS(Data-Strobe) エンコード方式を物理コーディングに採用している 1394 Bus ではケーブルを介して接続される対向ノード間で基準グランド電位がダイレクト接続されます。すなわち物理層 IC(PHY) - 1394 ケーブル - PHY は DC 接続されます。このため基準電位の異なるシステム機器同士を 1394 ケーブルで接続する場合は、商用 AC 電源系と 1394 物理層系の電源をアイソレートする必要があります。

システム機器の電源設計に依らず 1394 Bus を使用できるよう PHY-Link インターフェースはアイソレーション回路の使用を想定して設計されています。IEEE P1394a Draft Ver2.0 にアイソレーションバリアの回路例が掲載されています。MD8405 はこの P1394a Draft Ver2.0 タイプのアイソレーション回路をサポートしており、他のアイソレーション方式には対応していません。また、このアイソレーション回路を使用するためには Link コントローラ IC 側も P1394a Draft Ver2.0 タイプのアイソレーション回路をサポートしている必要があります。なお、アイソレーション回路を使わずに Link コントローラ IC とダイレクト接続する場合は上記の制限はありません。

図 5-10 IEEE P1394a Draft Ver2.0 アイソレーションバリア (一例)

図 5-10 に IEEE P1394a Draft Ver2.0 に掲載されているアイソレーションバリア回路の一例を示します。ここではこの容量タイプのアイソレーションバリアについて動作説明をします。P1394a Draft Ver2.0 には他にトランスタイプのアイソレーションバリアも掲載されています。使用される部品の耐圧の観点から一般的にトランスタイプの方がより大きなグランド電位差での使用に耐えますが、部品サイズの観点からは容量タイプの方がより小さいボードエリアに実装できます。動作原理自体は同一です。

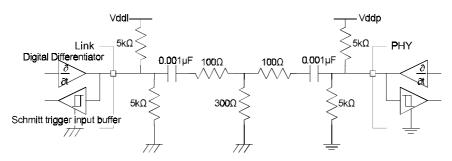

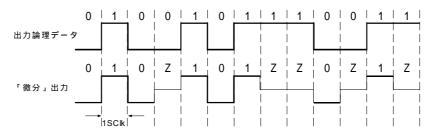

まず、IC 内部の出力部前段には図 5-10 に示されるような「ディジタル微分回路」があり、出力論理データ列が 0 から 1 へ、あるいは 1 から 0 へ変化するサイクルのみ実際にインターフェイスを「ドライブ」します。出力論理データ列が変化しないサイクルでは(1 が連続する場合、0 が連続する場合)、Z (ハイインピーダンス)状態を保ちます。図 5-11 に微分回路通過前後の波形変化の一例を示します。

図 5-11 ドライバ回路「微分」出力波形

一方 IC 内部の入力部は入出力特性にヒステリシスを持ったいわゆるシュミットトリガバッファで構成され、上記の微分波形が再びシュミットトリガバッファ通過後に元の論理データ列に再生されます。

このように、アイソレーションバリア回路を使うために上記の「ディジタル微分回路」および「シュミットトリガバッファ」が PHY IC、Link コントローラ IC 共に必要です。なお、アイソレーション回路を使わずダイレクト接続される場合は微分回路がバイパスされ、元の出力論理データ列がそのままインターフェイスに出力されます。

図 5-10 には  $100\Omega$  のシリーズ抵抗が PHY、Link 両側に入っていますが、これは通常片側にのみ必要で両 IC の電源電圧の差を吸収するアッテネータの役目を果たします。MD8405 は 3.3V 駆動のため、5V 駆動の Link コントローラを使用する場合のみ Link IC 側に  $100\Omega$  を接続します。これにより Link PHY 方向のドライブ波形はアッテネートされ、PHY Link 方向はほぼ 3.3V 振幅のまま伝達されます。このシリーズ抵抗はピン容量等の寄生容量と共に RC 遅延の主な要因となります。3.3V 駆動の Link コントローラを使用する場合はシリーズ抵抗は不要です。

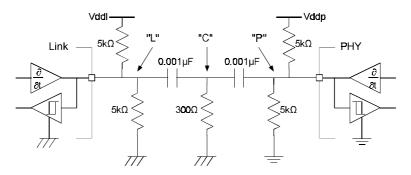

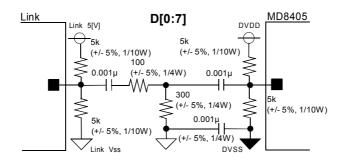

続いて図 5-12 を使って具体的な回路動作を説明します。

図 5-12 アイソレーションバリア回路

ここでは簡単のため PHY - Link 間のグランド電位差が 0V、PHY、Link 共 3.3V 動作と仮定します。DC 電位差は  $0.001\mu$ F 容量に常に蓄えられるため AC 動作を考える上では電位差 0V の場合と全く同一です。

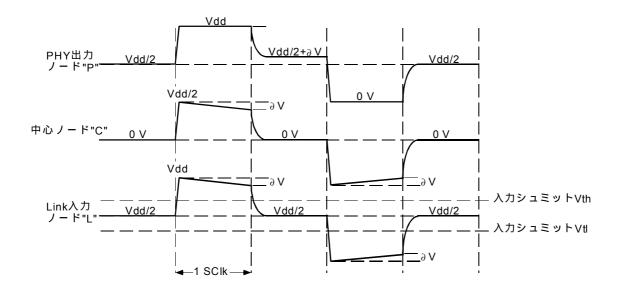

まず PHY、Link 両 IC が Z (ハイインピーダンス)出力状態の時、PHY IC の入出力ピン(以降ノード "P")及び Link IC 入出力ピン(以降ノード "L")はそれぞれ 5 k $\Omega$  の抵抗分割によって Vdd/2 に保たれます。(このとき内部ではシュミットトリガバッファにより、Z になる前の論理レベルが引き続き「受信」されています。)

一方、残る中心(Center)ノード(以降ノード "C")は300Ωにより 0V に保たれています。

図 5-13 各ノードの波形例

次に PHY が 1 をドライブすると、ノード "P" は Vdd に保持されます。この Vdd/2 Vdd の電位変化は ノード "C" さらにノード "L" に伝達され、ノード "C" は 0 Vdd/2 に、ノード "L" は Vdd/2 Vdd へと立 ち上がります。 ノード "P" は論理 1 すなわち電位 Vdd を 1 サイクル保持します。 ノード "C" は 300 $\Omega$  により放電されますがこの時の時定数は 300 $\Omega$  >0.001 $\Omega$  =0.3  $\Omega$   $\Omega$   $\Omega$  (これについては改めて説明します。) ノード "C" での波形はノード "L" にそのまま伝達され、結局 PHY がドライブした Z 1 のステップ波形がほぼ 保たれたまま Link に伝達されます。

次のサイクルで送るべき出力論理データが 0 の場合は上記に続いてノード "P" が Vdd=0 と変化し、同様の動作によりノード "C" は Vdd/2=Vdd/2 に、ノード "L" は Vdd=0 と変化します。

逆に、次のサイクルで送るべき出力論理データが 1 で前のサイクルと同一の場合は(図 5-13 はこの場合を示しています)、前出の「ディジタル微分回路」により PHY は出力バッファを Z とします。このとき残る低インピーダンスノードは "C" のみであるため、ノード "C" が Vdd/2 0 と初期値に戻ることにより同様の電位変化がノード "P" (Vdd Vdd/2) およびノード "L" (Vdd Vdd/2) に反映されます。この時の時定数はピン容量を例えば 10~pF とすると  $2\times300[\Omega]\times10[pF]=6~nsec$  で、1~theta サイクル (=20~nsec) より十分小さく設定されています。ノード "L" は Vdd/2 に戻りますが入力部のシュミットトリガバッファにより引き続き論理レベル 1~theta を受信します。

ここで、厳密にはノード "C" は PHY が 1 をドライブしているサイクル中に放電により ∂V 電圧降下しています。このためノード "C" が初期値 0V に戻る際の振幅は Vdd/2 - ∂V で、ドライブ側ノード "P" は Vdd Vdd/2 + ∂V となり、初期値 Vdd/2 まで戻りません。( 受信側ノード "L" は Vdd/2 まで戻ります。)

このズレ  $\partial V$  は次に PHY が 0 をドライブする際に相殺され(図 5-13 参照)、このズレが次々と蓄積されてゆくことはありません。(「ディジタル微分回路」により、1 SCLK サイクル 1 をドライブした後は次の 1 がドライブされる前に必ず 1 SCLK サイクルの 0 が入ります。)

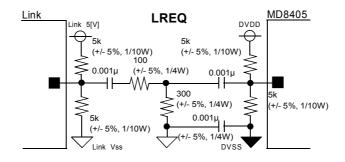

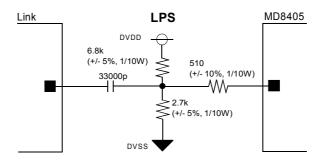

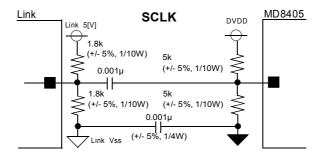

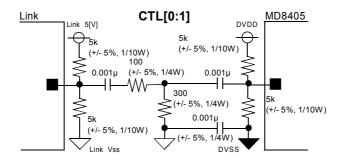

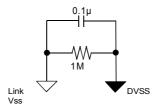

各 Link インターフェイスピンについてのアイソレーションバリア回路を図 5-14  $\sim$  図 5-19 に示します。

LREQ、CTL[0:1]、D[0:7] は上記 1394-1995 Annex J タイプのアイソレーションバリア回路を使用します。 デューティー 50% のクロック波形となる LPS、SCLK は比較的簡単な AC 接続回路を使用します。

LPS 入力部は CMOS 受けで、Link IC からのクロックが停止すると外部抵抗により CMOS 入力閾値以下となり "L" 期間が 2.56μsec 連続すると LPS="L" と認識します。逆に "H" 期間が 80n sec 連続すると LPS="H" と認識します。

SCLK は AC 接続の場合 Link IC 側にシュミットトリガ入力バッファが必要です。MD8405 側は CMOS 出力です。

図 5-14 LREQ アイソレーションバリア回路

図 5-15 LPS アイソレーションバリア回路

図 5-16 SCLK アイソレーションバリア回路

図 5-17 CTL[0:1] アイソレーションバリア回路

図 5-18 D[0:7] アイソレーションバリア回路

図 5-19 VSS 接続

図 5-14 (LREQ)、図 5-17 (CTL[0:1])、図 5-18 (D[0:7]) で、Link 側に直列に入っている  $100\Omega$  抵抗は、接続される Link チップが 5V 電源電圧の場合のみ必要で、Link チップが 3.3V 電源電圧の場合は不要です。

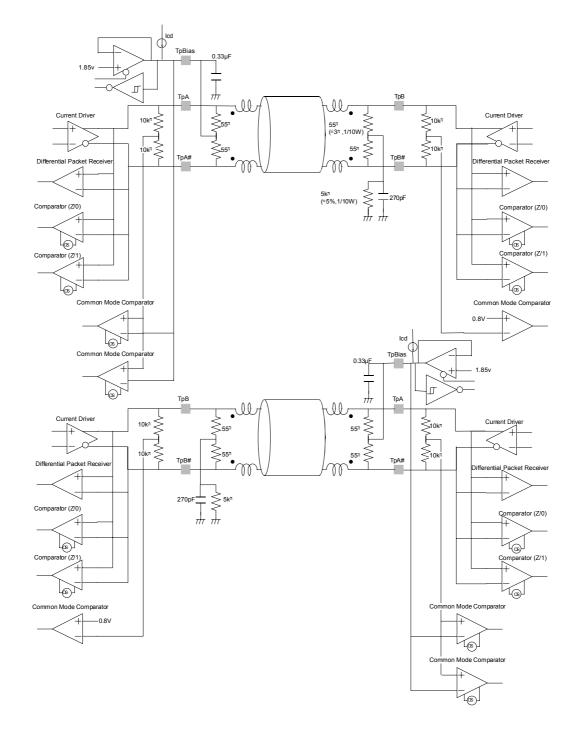

## 5-2 ケーブルインターフェイス

## 5-2-1 ケーブルインターフェイス回路

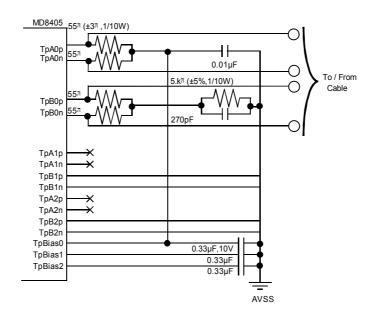

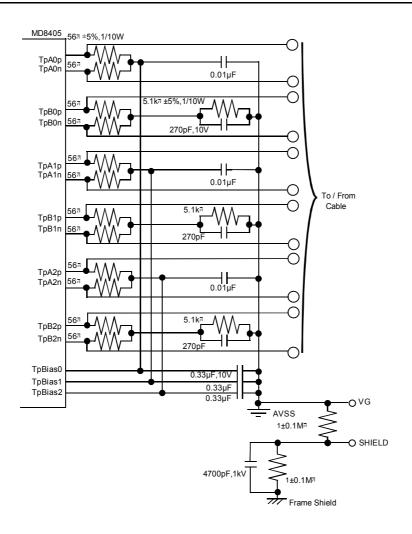

図 5-20 にケーブルインターフェイスの接続回路を示します。

図 5-20 ケーブルインターフェイス

ケーブルメディアとしては IEEE 1394 専用ケーブルが使われ、データ送受信は 2 組のシールドされたツイストペア線で行われます。図 5-20 に示されるように各ツイストペア線は自ノードの TpA ペアが対向ノードの TpB ペアに接続されます。

TpA、TpB 側共にケーブルインピーダンスに合わせた終端抵抗  $55\Omega(\pm 3\Omega, 1/10W) \times 2$  が必要です。この終端抵抗から IC のピンまでは最短になるよう配置して下さい。

TpA 側にはケーブルの同相 DC 電位を設定するため TpBias (標準 1.85V) が終端抵抗中間ノードに接続されます。TpBias にはデカップル用に  $0.33\mu F$  を接続して下さい。後述のスピードシグナルのための同相電流はここから供給されます。なお、このコンデンサは内部オペアンプの位相補償目的もあるため、実際にTpBias を使わない場合 (未使用ポートなど)にも必要です。

TpB 側には  $5 \text{ k}\Omega(\pm 5\%, 1/10\text{W}) // 270 \text{ pF}(10\text{V})$  を終端抵抗中間ノードに接続しプルダウンして下さい。これによりケーブルが抜かれ対向ノード TpA からの DC バイアスが断たれた際、TpB 側の DC 電位が 0V 近くまでドロップし同相コンパレータでこれを検知することが出来ます。270 pF はデカップル用です。

図 5-18 において終端抵抗 - ケーブル間に置かれたバランは同相信号の帯域制限をするためのコモンモードコイルです (250nH、K>0.97)。使用する場合はこの位置に接続して下さい。信号変化点で発生する同相ノイズによる電磁輻射 (EMI)を低減する効果があります。データ送受信には影響ありませんので、使用しなくても通信上の問題はありません。

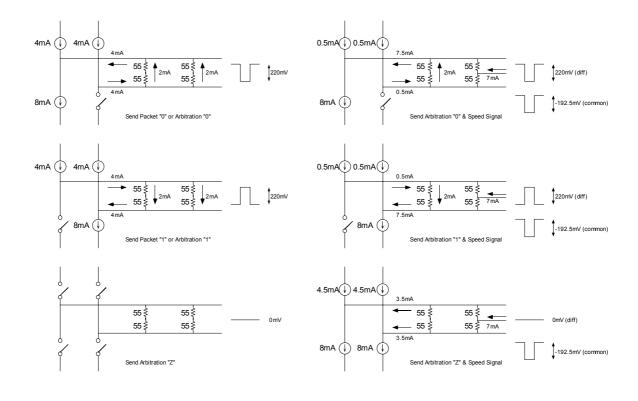

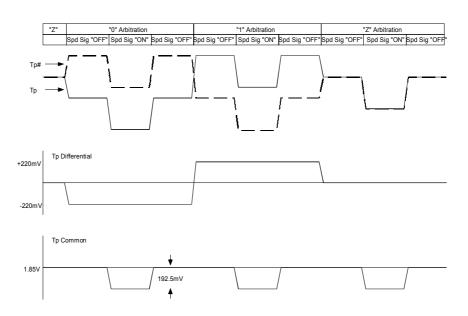

#### 5-2-2 ケーブルインターフェイス動作概要

対向ノード間での通信フェーズは大きく「アービトレーション」と「データパケット送受信」に分けられます。アービトレーション送受信は "0"、"1"、"Z" の 3 値論理(差動)で全二重通信で行われ、スピードシグナル(同相)はこれに重畳されます。パケット送受信は "0"、"1" の 2 値論理(差動)で半二重通信で行われます。いずれの場合も送信はハイインピーダンス電流ドライバによって、受信は終端抵抗両端の差動電圧あるいは同相電圧をコンパレータ、パケットレシーバで検出することによって行われます。

TpA、TpB それぞれで送受信される信号の内訳は以下のようになります。

TpA: 差動信号 アービトレーション送受信、パケット送信(Strobe 信号)、パケット受信

(Data 信号)

同相信号 スピードシグナル受信

ケーブルバイアス (TpBias)

TpB: 差動信号 アービトレーション送受信、パケット送信 ( Data 信号 )、パケット受信

(Strobe 信号)

同相信号 スピードシグナル送信

コネクトステータス検出

図 5-21 に各種データ送信時の電流ドライバの状態、ケーブル上の電流、終端抵抗で観測される差動・同相電圧波形の例を示します。(図 5-21 は各信号状態の説明図であり、ある特定のバスフェーズでの波形をしめすものではありません)(ここでは S200 スピードシグナルを例に説明しています)

図 5-21 ドライバ電流と出力波形 (S200 スピードシグナル時)

#### 5-2-3 ポートステート

MD8405 は P1394a Draft Ver2.0 に準拠しています。P1394a Draft Ver2.0 では各ポートには次の 4 つの状態 が定義されています。

: このポートは TpBias および TpA/TpB に信号を出力しません。また、Bias および TpA/ - Disabled

TpB に入力される信号を検出しません。このポートではコネクト検出回路のみが動作

しています。

コネクト検出回路でケーブル接続状態の変化を検出した場合、int enable ビットが セットされていれば、上位層に対して Status/LinkOn によるインタラプトを出力しま

- Disconnected :このポートには他ノード PHY との物理的なケーブル接続がなく、TpBias および TpA/

TpB に信号を出力しません。また、Bias および TpA/TpB に入力される信号を検出し

ません。このポートではコネクト検出回路のみが動作しています。

- Suspended : このポートには他ノード PHY との物理的なケーブル接続はありますが、TpBias およ

び TpA/TpB に信号を出力しません。また、TpA/TpB に入力される信号を検出しませ ん。このポートではバイアス検出回路、コネクト検出回路のみが動作しています。

:このポートには他ノード PHY との物理的なケーブル接続があり、TpBias および TpA/ - Active

TpBに信号を出力します。また、BiasおよびTpA/TpBに入力される信号を検出します。

MD8405 は Suspended、Disabled、Disconnected 状態のポートの消費電力を Active 状態のポートの消費電 力に比べて低下します。

また、MD8405 は 3 ポートすべてが Active 状態以外であり、かつ LPS 信号が Low で Link が非アクティ ブである場合には、自動的に低消費電力モードに入ります。低消費電力モード時は通常動作時と比べて消 費電力が大幅に低下されます。(6-3DC 特性参照)

#### 5-2-4 コネクト検出回路

MD8405 には物理的なケーブル接続を検出するために、コネクト検出回路を内蔵しています。この回路 はこのポートがTpBiasを出力していない期間、ポートへの物理的な接続の有無を検出します。

#### 5-2-5 Suspend/Resume

Active な状態から Suspended 状態への遷移には2通りの動作があります。

1 つはこのノードのあるポートに対する suspend ビットが設定された Remote Command パケットを送受 信した場合です。Remote Command パケットは、このノードのローカルな Link から送信される場合と、そ れ以外のノードから送信される場合がありますが、どちらの場合にも MD8405 は Remote Command パケッ トの送受信後、すべてのポートに RemoteConfirmation パケットを送信し、その後 suspend ビットがセット されたポート (Suspendinitiator) 以外のポートにバスリセット信号を出力し、このノードはバスリセット状 態に入ります。同時に Suspend initiator ポートには TX SUSPEND を出力し、このポートは Suspended 状態 へ遷移していきます。

もう1つはSuspend initiatorの出力したTX SUSPENDを受信した場合(RX SUSPEND)です。RX SUSPEND を受信したポート (Suspend target) はその後 Suspended 状態へ遷移していきます。またこのノードは RX SUSPEND を受信したポート以外の Active なポートに TX SUSPEND を出力し、Suspend initiator にしま す。この Suspend initiator ポートもその後 Suspended 状態へ遷移します。

このようにリーフノードまで Suspended 状態は伝播していきますが、途中に IEEE Std1394-1995 ノード、 Disabled ポート、Suspended ポートがある場合、Suspended 状態の伝播はそこで止まります。

ポートが Suspended 状態に入ってもなお対向ポートの Bias を検出している場合には Fault ビットをセッ トし、正常に Suspended 状態に入っていないことを示します。

Suspended 状態のポートは次の場合に Resume 動作を開始し、Active 状態に遷移します。

- Fault ビットがクリアされており、Bias を検出した場合。

- Resume パケットを送受信した場合。

- このポートに対する resume ビットが設定された Remote Command パケットを送受信した場合。

また、Boundary ノードではない場合に、Suspended 状態もしくは Disconnected 状態のポートが Resume パケット、Remote Command パケット送受信以外の理由で Resume 動作を開始すると、このノードの他の Suspended ポートも同時に Resume 動作を開始します。

Resume 動作は TpBias を出力し、対向ポートからの Bias を検出すると正常に終了し、Active 状態に遷移します。しかし、対向ポートからの Bias を検出できない場合には Fault ビットをセットし、再び Suspended 状態に戻り、正常に Resume 動作が終了しなかったことを示します。

#### 5-2-6 Suspend/Resume オフモード (SR 端子 ="L")

Suspend/Resume 機能を使用しないモードでは MD8405 は次の動作をします。

- Remote Command パケットを無視します。

- Resume パケットを無視します。

- PHY レジスタの Disabled、int enable、Resume int ビットを無視します。

- コネクトは Bias で検出します (P1394a Draft Ver1.3 準拠)。

```

void connection_status() { // Continuously monitor port status in all states

int i;

isolated node = TRUE; // Assume true until first connected port found

for (i = 0; i < NPORT; i++) {

isolated node &= !connected[i];

if (connection in progress[i]) {

if (!port_status[i])

connection_in_progress[i] = FALSE; // Lost attempted connection

else if (connect_timer >= (isolated_node) ? 2 * CONNECT_TIMEOUT :

CONNECT TIMEOUT) {

connection in progress[i] = FALSE;

connected[i] = TRUE; // Confirmed connection

if (isolated node) // Can we arbitrate?

ibr = TRUE; // No, transition to R0 for reset

else

isbr = TRUE; // Yes, arbitrate for short reset

} else if (!connected[i]) {

if (port_status[i]) { // Possible new connection?

connect_timer = 0; // Start connect timer

connection_in_progress[i] = TRUE;

}

} else if (!port_status[i]) { // Disconnect?

connected[i] = FALSE; // Effective immediately!

if (child[i]) // Parent still connected?

isbr = TRUE; // Yes, arbitrate for short reset

else

ibr = TRUE; // No, transition to RO for reset

}

```

- ポートの状態は Disconnected(!Connected) と Active(Connected) のみです (P1394a Draft Ver1.3 準拠 )。 どちらの状態においても TpBias には 1.85V が出力されます。ただし、ハードウエアリセット期間、 TpBias はプルダウンされます。

#### 5-2-7 低消費電力 (Power Down) モード

PoweDown に入る条件は

- 1) LPS が L で Link が非アクティブである場合でかつ、

- 2) LinkOn の出力をしていない場合でかつ、

- 3) すべてのポートが Disconnected, Suspended, Disabled の状態にある場合。 これらの条件を満たしてから 680ms 待って Power Down する。

#### また、復帰する条件は

- 1) LPS が H になったとき、または

- 2) CPS の低下を検出したとき、または

- 3) Disconnected のポートに Connect を検出したとき、または

- 4) Suspended のポートに!Connect を検出したとき、または

- 5) Suspended のポートに Bias を検出したとき、または

- 6) Suspended で、Suspend fault のポートに Bias を検出したとき、または

- 7) Disabled で、Int\_enable のポートに Connect の変化を検出したときです。

復帰したとき約 11~12μs 後に通常動作に復帰します。

動作は PowerDown していなかったように動作しますが、復帰条件が上の場合は、次の動作をします。

- 1) LCLK 出力

- 2) LinkOn(Interrupt)

- 3) connection status(), P0:P1

- 4) connection status(), P5:P0

- 5) connection\_status(), P5:P1

- 6) connection status(), P5:P5

- 7) LinkOn(Interrupt)

です。

#### 5-2-8 S200 モード (S200 端子="H")

S200 モードで MD8405 は次の動作をします。

- MD8405 が送信する Self-ID パケットの sp ビットに "01" を出力し、このノードの最高動作 周波数が 196.608Mbit/s であること示します。

- PHY レジスタ Max\_speed ビットに "001" を出力し、このノードの最高動作周波数が196.608Mbit/s であること示します。

- Self-ID 期間に S200 のスピードシグナルを出力し、このノードの最高動作周波数が 196.608Mbit/s であること示します。

このモードでは D[4:7] 端子は NC として使用してください。 このモードでは LREQ 端子から 400 Mbps のバスリクエストを入力しないでください。

#### 5-2-9 CPS (ケーブルパワーステータス)

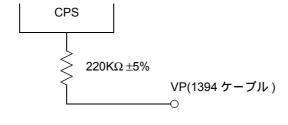

CPS ピンは外部抵抗 Rcps (通常  $226k\Omega$ )を介してケーブルパワー (Vp)に接続します。ケーブルパワー が閾値 (通常 7.5V)以下に低下したことを検出します。使用しない場合は、AVDD に接続します。

検出閾値 Vt と外部抵抗 Rcps との関係は以下の式になります。

$Vt=1.85+Rcps\times25\mu$

#### 5-2-10 未使用ポートの処理

MD8405 には、ポートが 3 つあります。このうち、2 ポートしか使用しない場合、1 ポートしか使用しない場合は、未使用ポートの端子を次のように接続します。

| 未使用ポートの端子名 | 接続                 |

|------------|--------------------|

| TpAp, TpAn | ノンコネクト             |

| ТрВр, ТрВп | AVSS               |

| TpBias     | 0.33µF を介して AVSS へ |

表 5-13 未使用ポート端子の処理

例として、1ポートのみ使用する場合の回路図を示します。

図 5-22 1ポートのみ使用時回路図

#### 5-3 クロック回路

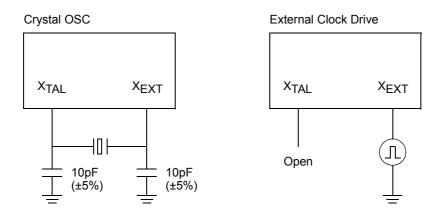

#### 5-3-1 クリスタルオシレータ

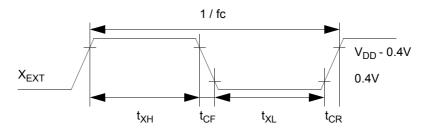

オシレータ出力周波数は、 $24.576 MHz \pm 100 ppm$  が必要です。クリスタル自身は、10 pF の負荷容量を接続した状態で  $\pm 50 ppm$  の精度が必要です。

図 5-23 クロック回路

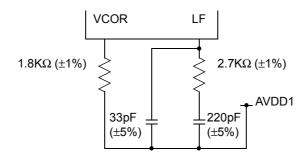

#### 5-3-2 PLL

PLL は、水晶発振子の出力の 24.576Mhz から 16 倍の 393.216Mhz をつくります。 PLL のロックタイムは、100μsec 以下です。

図 5-24 PLL 外部回路

#### 5-4 外部回路

### 5-4-1 CPS 端子

図 5-25 CPS 外部回路

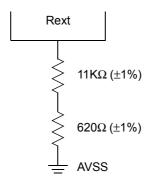

# 5-4-2 Rext 端子

図 5-26 Rext 外部回路

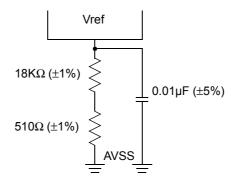

## 5-4-3 Vref 端子

図 5-27 Vref 外部回路

#### 5-5 ハードウェアリセット

Purb 端子に  $0.1\mu F$  の外部キャパシタを経由してグランドに接続することによって電源投入時に最小 15 msec のリセット幅を発生させます。この端子に "L" レベルを外部から印加することによりすべてのステートマシーンをリセットします。

この時のケーブルインターフェイスの動作は以下のとおりになります。

- 1) MD8405 は Purb が "L" の期間 TpBias に 0V(Pull Down) します。

- 2) リセット終了後 CONNECT\_TIMEOUT 時間ケーブルの物理的な接続を確認します。この間 TpBias は HiZ 状態です。

接続が確認されなかったら 3) へ。(Port connection state machine では P0)接続が確認されたら 4) へ、(Port connection state machine では P0:P1)

- 3) Disconnected。Connect 検出回路のみ動作中

- 4) リジュームします。TpBias に 1.85V を出力し、BIAS\_HANDSHAKE 期間相手ノードからの Bias を待ちます。

BIAS\_HANDSHAKE期間中に相手からのBiasを検出すると5)へ。(Port connection statemachineではP1:P2)

BIAS\_HANDSHAKE 期間中に相手からの Bias を検出しないと 6) へ。(Port connection statemachine ではP1:P5)

- 5) 次のバスリセットから通常動作を開始します (Active)。Bias 検出回路が動作しています。

- 6) Suspended。TpBias に 0V(Pull down) しその後 TpBias を HiZ にし、connect 検出回路を動作します。Bias 検出回路も動作しています。

# 6 電気特性

# 6-1 絶対最大定格

(VSS=0V)

|      |      |              | ( |

|------|------|--------------|---|

| 記号   | 項目   | 項目 定格        |   |

| VDD  | 電源電圧 | -0.5~5.0     | V |

| VIN  | 入力電圧 | -0.5~VDD+0.5 | V |

| Vout | 出力電圧 | -0.5~VDD+0.5 | V |

| Tstg | 保存温度 | -65~150      |   |

表 6-1 絶対最大定格

## 6-2 推奨動作条件

| 記号   | 項目   | 定格      | 単位 |

|------|------|---------|----|

| VDD  | 電源電圧 | 3.0~3.6 | V  |

| VIN  | 入力電圧 | 0~VDD   | V  |

| Vout | 出力電圧 | 0~VDD   | V  |

| TA   | 周囲温度 | 0~70    |    |

表 6-2 推奨動作条件

## 6-3 DC 特性

推奨動作条件下での電気特性 (特記なき場合)

(VSS=0V)

|       |                    |                           |                     |           |     | (VSS=0)   | ,     |

|-------|--------------------|---------------------------|---------------------|-----------|-----|-----------|-------|

| 記号    | 項目                 | 端子                        | テスト条件               | MIN       | TYP | MAX       | 単位    |

| VT+   | 入力シュミット            | LREQ, CTL[0:1],           |                     | VDD/2+0.3 |     | VDD/2+0.8 | V     |

| \/-   | 立上りしきい値            | D[0:7]                    |                     |           |     |           |       |

| VT-   | 入力シュミット            | LREQ, CTL[0:1],<br>D[0:7] |                     | VDD/2-0.8 |     | VDD/2-0.3 | V     |

| VIH   | 立下りしきい値<br>"H" レベル | LPS, LDSEL, DIRECT,       |                     |           |     |           |       |

| VIII  | 入力電圧               | PC[0:2], Disabled[0:2],   |                     |           |     |           |       |

|       | 八八电压               |                           |                     | VDD-1.0   |     |           | V     |

|       |                    | En_Accel, En_Multi,       |                     |           |     |           |       |

|       |                    | CMC, XEXT                 |                     |           |     |           |       |

| VIL   | "L" レベル            | LPS, LDSEL, DIRECT,       |                     |           |     |           |       |

|       | 入力電圧               | PC[0:2], Disabled[0:2],   |                     |           |     |           |       |

|       |                    | En_Accel, En_Multi,       |                     |           |     | 1.0       | V     |

|       |                    | CMC, XEXT                 |                     |           |     |           |       |

| IIН   | "H" レベル            | LREQ, CTL,                | VIH=VDD             | -10       |     |           |       |

|       | 入力電流               | D[0:7]                    | VIII- V DD          | -10       |     |           |       |